TKR-740

35

CIRCUIT DESCRIPTION

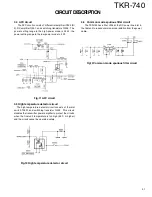

4.4 Receiver main PLL circuit

The receiver main PLL circuit consists of VCO (Q8, Q9)

and a single-chip PLL IC IC1, buffer amplifier Q14, RF amplifier

Q3, Q1, Q5, and Q6. The first local oscillator is an upper

heterodyne local oscillator, and the VCO oscillator frequency

is 202.850 to 218.850 M Hz. In addition, the tw o VCOs cover

Fig.17 Receiver main PLL circuit

tw o bands: the Q8 VCO covers the low er band and the Q9

VCO covers the upper band. PLL IC1 compares the 4.5M Hz

signal from the receiver DDS circuit and the VCO signal w ith

the 100kHz comparison frequency.

Summary of Contents for TKR-740

Page 97: ...TKR 740 TKR 740 BLOCKDIAGRAM 121 122 ...

Page 99: ...TKR 740 TKR 740 INTERCONNECTION DIAGRAM 125 126 ...

Page 101: ...MEMO 129 ...