Keysight M8132A 640 GSa/s Digital Signal Processor User’s Guide

43

Control In / Out

4

The Control In/Out (0..9) port is separated in 5 inputs (Control In (0..4)) and

5 outputs (Control Out (5..9)). Each multiplexer has a separate clear

mechanism that sets all outputs of the corresponding multiplexer to zero.

Additionally, it is possible to disable the output ports of Control Out (5..9).

This sets the ports to “high impedance”.

All input sources for each multiplexer can be routed to each output. The

switch matrix is clocked with a 200 MHz clock, and therefore all inputs are

synchronized to this clock. After input synchronization, the transmission is

cycle accurate.

Example: When routing the Control In (0) to both FPGAs, the connected

signal is synchronized to the 200 MHz clock. So, there is an input accuracy

of 5ns. Once synchronized to this clock, the transmission is cycle accurate,

which means that the connected signal information will arrive at the

sandbox port of both FPGAs at the same time.

The LOOP_BACK (1..0) connection allows to transfer of information

between the two FPGA sandboxes synchronously.

Input Multiplexer of the Switch Matrix

Four bits are used to select the source for each output of the input

multiplexer. The corresponding bit positions inside the selector field in the

soft front panel are specified in the following table.

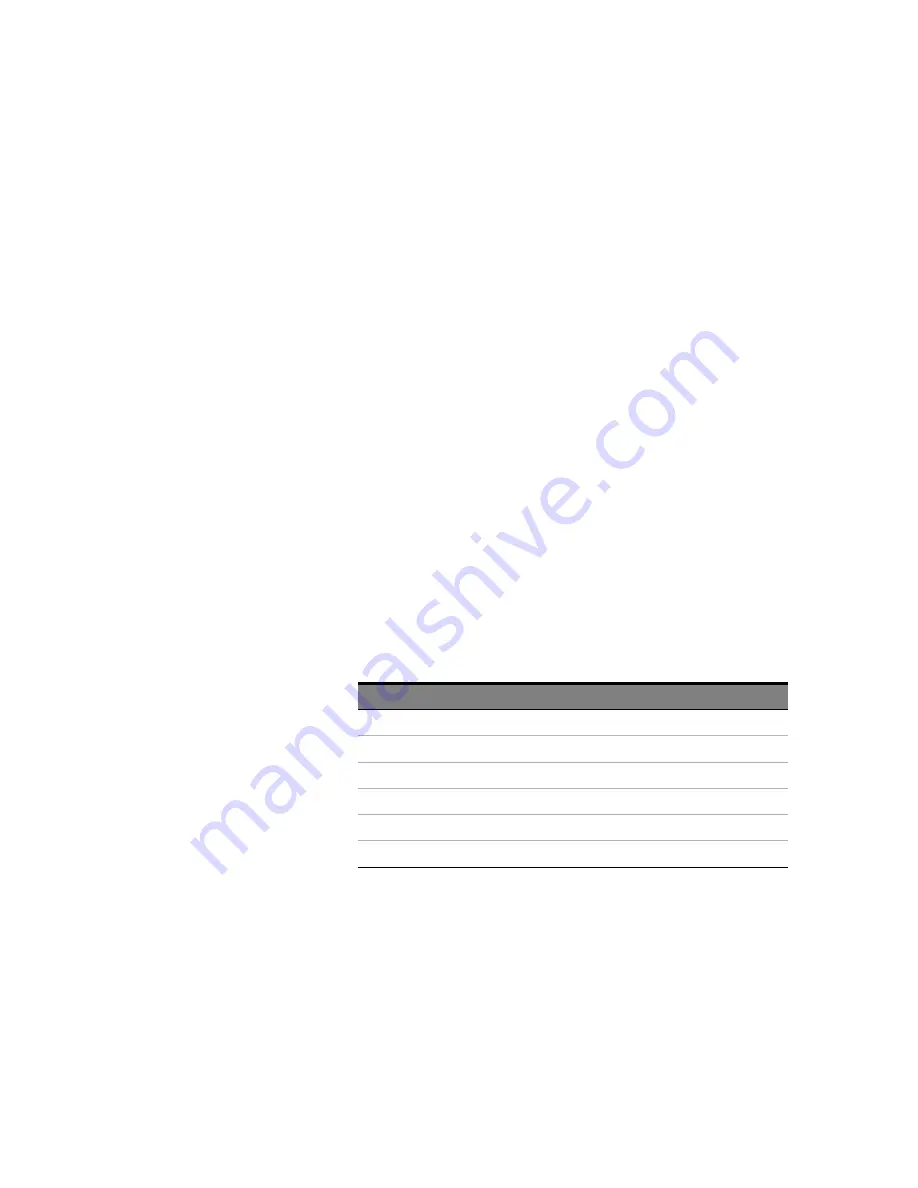

Table 4

Bit Positions for Output Ports of the Input Multiplexer of the Switch Matrix

Bit Positions

Output Port

23..20

GP_TRIG_IN_B(2)

19..16

GP_TRIG_IN_B(1)

15..12

GP_TRIG_IN_B(0)

11..8

GP_TRIG_IN_A(2)

7..4

GP_TRIG_IN_A(1)

3..0

GP_TRIG_IN_A(0)