VITA 57 Development Kit User's Guide

Additional Information

SD.DT.F79-0e

Page

19

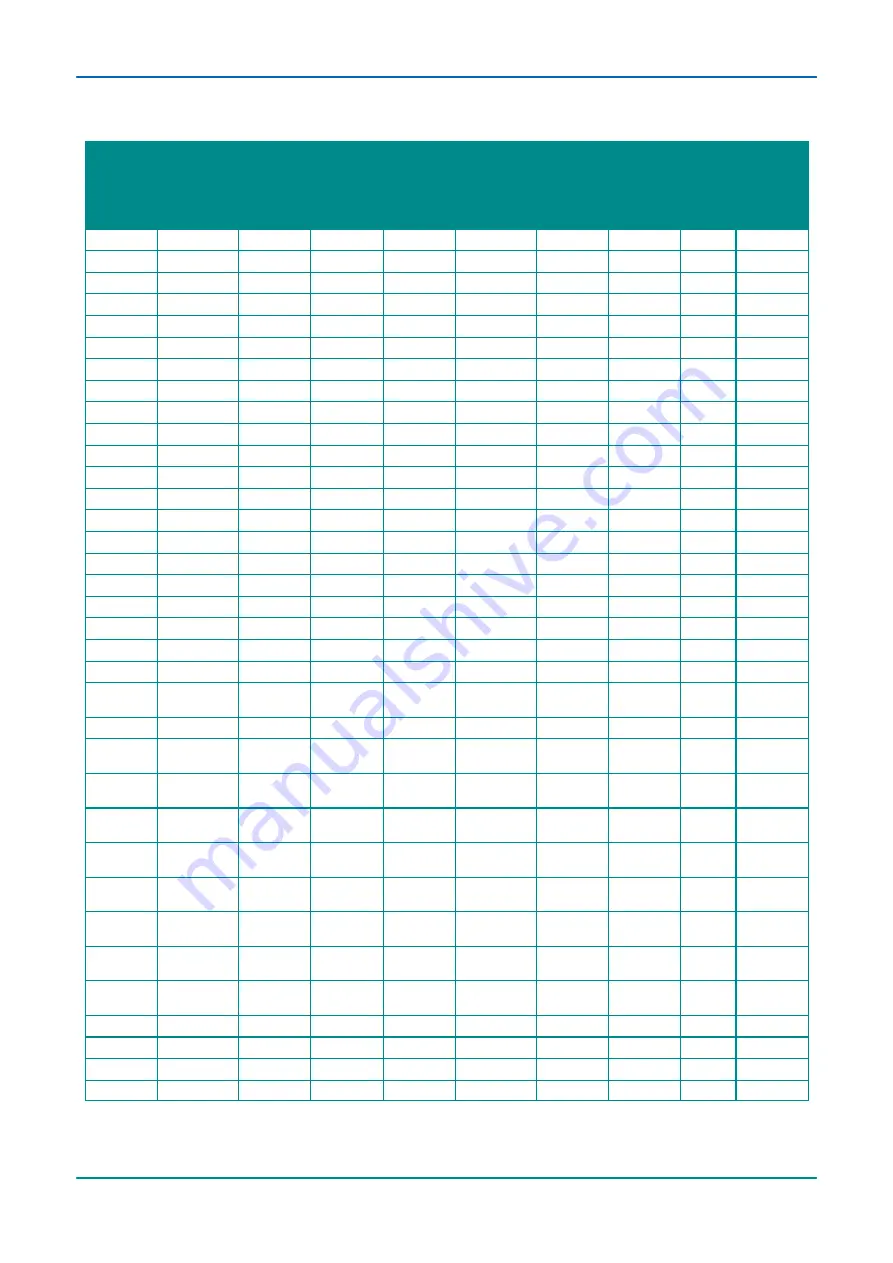

Test

loopback

connector

on RTM

J14

RTM

J14 pin

VM6250

VME P2

connector

pin

VM6250

PMCB_IO

signal

FMC

connector

pin to

VM6250

(VITA57 /

schematics)

FMC-SER

0 signal to

VM6250

FMC-SER

0 I/O name

FMC-SER

0 signal

from

VM6250

FMC

connector

pin from

VM6250

(VITA57 /

schematics)

FPGA pin

A17

H23 / 228

LA19N

GPIO6

HB13N

E31 / 305

32

A16 (1)

32

A11

G21 / 207

LA20P

GPIO7

HB2P

F22 / 216

42

A20

42

1k to pin 44

A12

G22 / 217

LA20N

GPIO8

HB2N

F23 / 226

44

A21

44

B11

H25 / 248

LA21P

GPIO9

HB10P

K31 / 310

49

C25

49

1k to pin 50

C11

H26 / 258

LA21N

GPIO10

HB8P

F28 / 276

50

A25

50

B13

G24 / 237

LA22P

GPIO11

HB10N

K32 / 320

51

C26

51

1k to pin 52

A13

G25 / 247

LA22N

GPIO12

HB8N

F29 / 286

52

A26

52

B14

D23 / 224

LA23P

GPIO13

HB14P

K34 / 340

53

C27

53

1k to pin 55

A14

D24 / 234

LA23N

GPIO14

HB14N

K35 / 350

55

C28

55

D13

H28 / 278

LA24P

GPIO15

HB12P

F31 / 306

54

A27

54

1k to pin 56

D14

H29 / 288

LA24N

GPIO16

HB12N

F32 / 316

56

A28

56

E14

G27 / 267

LA25P

GPIO17

HB17P

K37 / 370

57

C29

57

1k to pin 59

F14

G28 / 277

LA25N

GPIO18

HB17N

K38 / 380

59

C30

59

E15

D26 / 254

LA26P

GPIO19

HB20P

F37/366

58

A29

58

1k to pin 60

D15

D27 / 264

LA26N

GPIO20

HB20N

F38 / 376

60

A30

60

E17

C26 / 253

LA27P

GPIO21

HB18P

J36/359

61

C31

61

1k to pin 63

E16

C27 / 263

LA27N

GPIO22

HB18N

J37 / 369

63

C32

63

F18

H31 / 308

LA28P

GPIO23

HB16P

F34 / 336

62

A31

62

1k to pin 64

F17

H32 / 318

LA28N

GPIO24

HB16N

F35 / 346

64

A32

64

N12

G18/177

LA16P

DXEN (2)

M11

G19 / 187

LA16N

DXEN1516

(2)

G14

G33 / 327

LA31P

LED1R_S

W1 (3)

G15

G34 / 337

LA31N

LED1G_S

W2 (3)

D12

G36 / 357

LA33P

LED2R_S

W3 (3)

E12

G37 / 367

LA33N

LED2G_S

W4 (3)

D18

G30 / 297

LA29P

CAN1_RX

D (4)

D17

G31 / 307

LA29N

CAN1_TX

D (4)

C18

H34/338

LA30P

CAN2_RX

D (4)

B18

H35 / 348

LA30N

CAN2_TX

D (4)

B16

H37 / 368

LA32P

CAN_STB

A16

H38 / 378

LA32N

TB0201

GND

HA18P

J18 / 179

5

C3

5