Lake Shore Model 642 Electromagnet Power Supply User’s Manual

5-4

Computer Interface Operation

Message Strings (Continued)

A query string is issued by the computer and instructs the instrument which response to send. Queries are issued similar

to commands with the computer acting as ‘talker’ and the instrument as ‘listener’. The query format is:

<query mnemonic><?><space><parameter data><terminators>.

Query mnemonics are often the same as commands with the addition of a question mark. Parameter data is often

unnecessary when sending queries. Query mnemonics and parameter data if necessary is described in Paragraph 5.3.

Terminators must be sent with every message string. Issuing a query does not initiate a response from the instrument.

A response string is sent by the instrument only when it is addressed as a ‘talker’ and the computer becomes the

‘listener’. The instrument will respond only to the last query it receives. The response can be a reading value, status

report or the present value of a parameter. Response data formats are listed along with the associated queries in

Paragraph 5.3.

5.1.4 Status

System

5.1.4.1 Overview

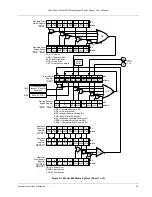

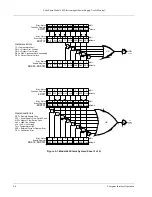

The Model 642 implements a status system compliant to the IEEE 488.2 – 1992 standard. The status system provides a

method of recording and reporting instrument information and is typically used to control the Service Request (SRQ)

interrupt line. A diagram of the status system is shown in Figure 5-1. The status system is made up of register sets, the

Status Byte register and the Service Request Enable register. Each register set consists of three types of registers,

condition, event, and enable,

5.1.4.1.1 Condition

Registers

Each register set (except the Standard Event Register set) includes a condition register as shown in Figure 5-1. The

condition register constantly monitors the instrument status. The data bits are real-time and are not latched or buffered.

The register is read-only.

5.1.4.1.2 Event

Registers

Each register set includes an event register as shown in Figure 5-1. Bits in the event register correspond to various

system events and latch when the event occurs. When an event bit is set, subsequent events corresponding to that bit are

ignored. Set bits remain latched until the register is cleared by a query command (such as *ESR?) or a *CLS command.

The register is read-only.

5.1.4.1.3 Enable

Registers

Each register set includes an enable register as shown in Figure 5-1. An enable register determines which bits in the

corresponding event register will set the summary bit for the register set in the Status Byte. The user may write to or read

from an enable register. Each event register bit is logically ANDed to the corresponding enable bit of the enable register.

When an enable register bit is set by the user, and the corresponding bit is set in the event register, the output (summary)

of the register will be set, which in turn sets the summary bit of the Status Byte register.

5.1.4.1.4

Status Byte Register

The Status Byte register, typically referred to as simply the Status Byte, is a non-latching, read-only register that contains

all of the summary bits from the register sets. The status of the summary bits are controlled from the register sets as

explained above. The Status Byte also contains the Request for Service (RQS)/Master Summary Status (MSS) bit. This

bit is used to control the Service Request hardware line on the bus and to report if any of the summary bits are set via the

*STB? command. The status of the RQS/MSS bit is controlled by the summary bits and the Service Request Enable

Register.

5.1.4.1.5

Service Request Enable Register

The Service Request Enable Register determines which summary bits in the Status Byte will set the RQS/MSS bit of the

Status Byte. The user may write to or read from the Service Request Enable Register. Each Status Byte summary bit is

logically ANDed to the corresponding enable bit of the Service Request Enable Register. When a Service Request

Enable Register bit is set by the user, and the corresponding summary bit is set in the Status Byte, the RQS/MSS bit of

the Status Byte will be set, which in turn sets the Service Request hardware line on the bus.