Appendix B

Watchdog Timer

Introduction

Most systems need to be self-reliant. It's not usually possible to wait for someone to reboot them

if there are some component wrong. Some system designs, such as space probes, are simply not

accessible to human operators. If the system ever hangs, such systems are permanently disabled.

In other cases, the speed with which a human operator might reset the system would be too slow

to meet the uptime requirements of the product.

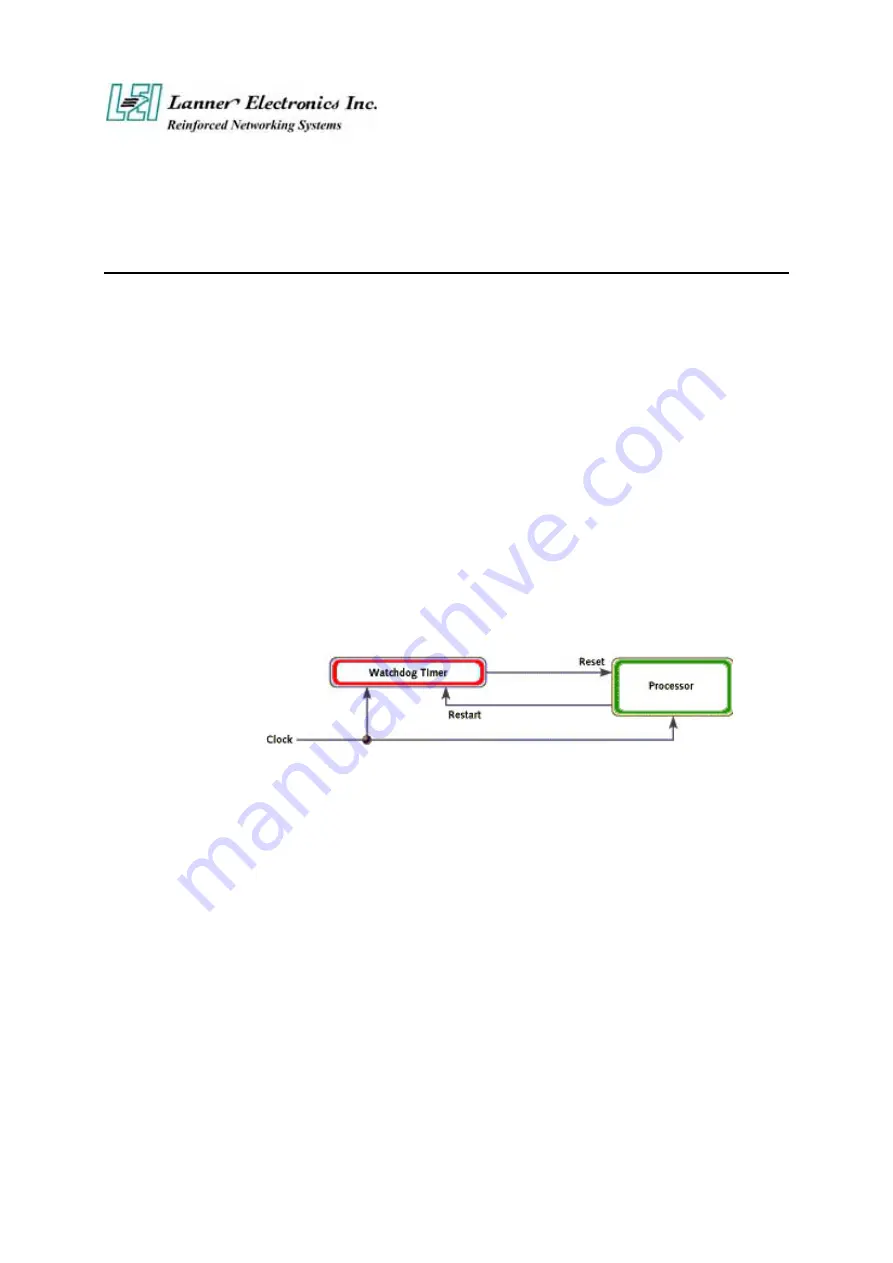

A watchdog timer is a piece of hardware that can be used to automatically detect system

anomalies and reset the processor if any occur. Generally speaking, a watchdog timer is based on

a counter that counts down from some initial value to zero. The software selects the counter's

initial value and periodically restarts it. If the counter ever reaches zero before the software

restarts it, the software is presumed to be malfunctioning and the processor's reset signal is

asserted. The processor will be restarted as if a human operator had cycled the power.

Detail Register, Bit, and Pin Descriptions

A watchdog action consists of a series of watchdog instructions. A watchdog instruction

is the operation on a register region. This section describes the detail register in LPC

I/O(IT8712F).

The feathers of Watch dog timer in LPC I/O (IT8712F) is as below description.

- Time resolution 1 minute or 1 second, maximunm 255 minutes or 255 seconds

- Output to KRST# when expired.

The Watch Dog Timer(WDT) function is constituted by a time counter, a time-out status

register, and the timer reset control logic. The time-out status bit may be mapped to an

interrupt or KRST# through the WDT Configuration register. The WDT has a

programmable time-out range from 1 to 255 minutes or 1 to 255 seconds. The units is

also programmable, either a minute or a second, via bit7 of the WDT Configuration

register. When the WDT Time-out Value register is set to a non-zero value, the WDT

loads the value and begin counting down from the value. When the value reaches to 0,