the WDT status register will set .

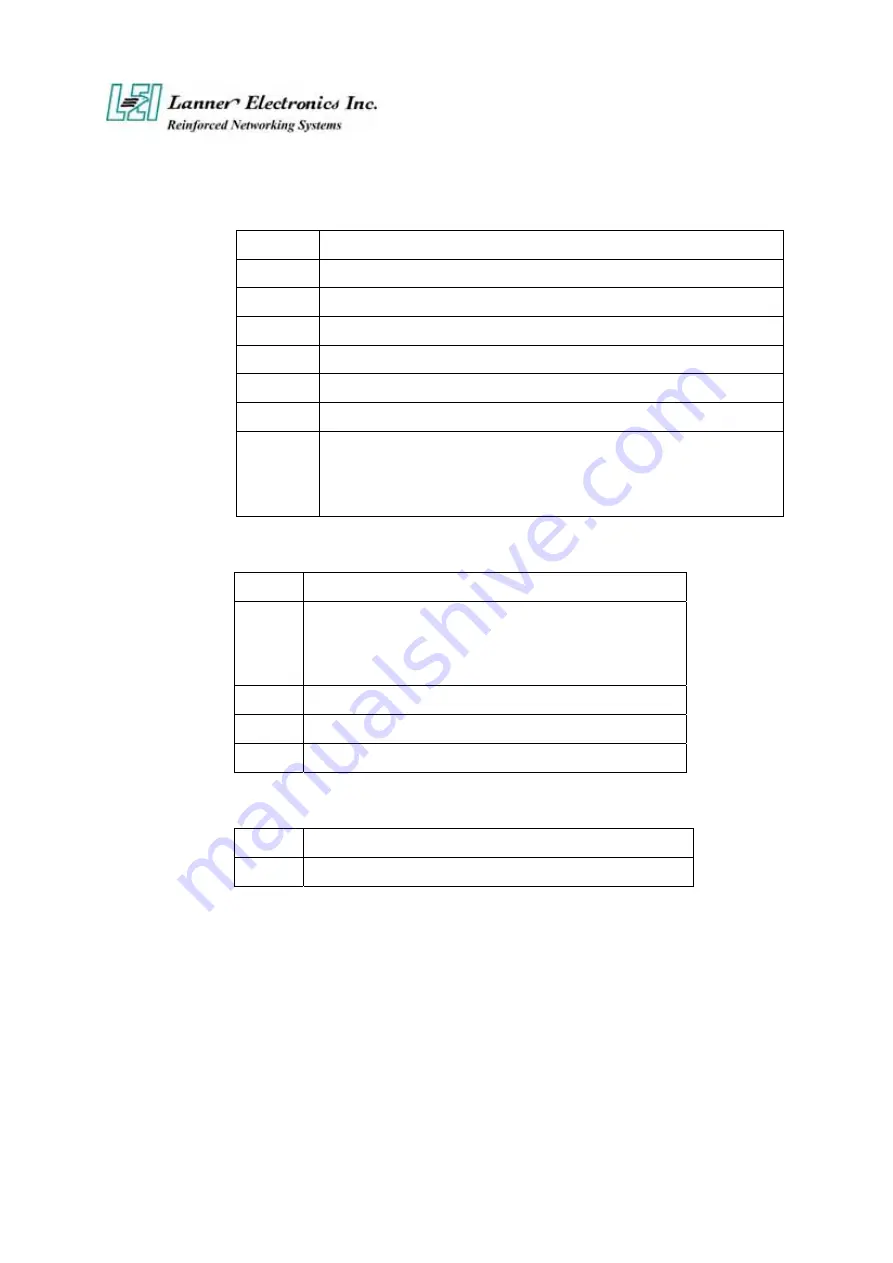

Watch Dog Timer Control Register (Index =71h, Default=00h)

Bit Description

7

WDT is reset upon a CIR interrupt

6

WDT is reset upon a KBC(mouse) interrupt

5

WDT is reset upon a KBC(keyboard) interrupt

4

WDT is reset upon a read or a write to the Game Port base address

3-2 Reserved

1

Force Time-out. This bit is self-clearing

0 WDT

Status.

1:WDT value reaches 0

0: WDT value is not 0

Watch Dog Timer Configuration Register (Index=72h, Default=00h)

Bit Description

7

WDT Time-out value select

1: Second

0: Minute

6

WDT output through KRST (pulse) enable

5-4 Reserved

3-0

Select the interrupt level for WDT

Watch Dog Timer Time-Out Value Register (Index=73h, Default=00h)

Bit Description

7-0

WDT time-out value 7-0

If you enable the watch-dog, the hardware timer will reboot your system if your

software encounters an unexpected error, or stops responding. The watch-dog timer

period (from enable to reset) was decided by the jumper setting of watch-dog time out

period. Please refer to the chapter on jumper settings and connectors. During the period

of enable to reset, you could still cancel reset by disabling the watch-dog.

Notes : Lanner provide the sample code in the Manual/Driver CD. The path is under

//FW-7650_MB-X71/Watchdog