MIPI D-PHY Bandwidth Matrix Table

User Guide

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

10

FPGA-UG-02041-1.1

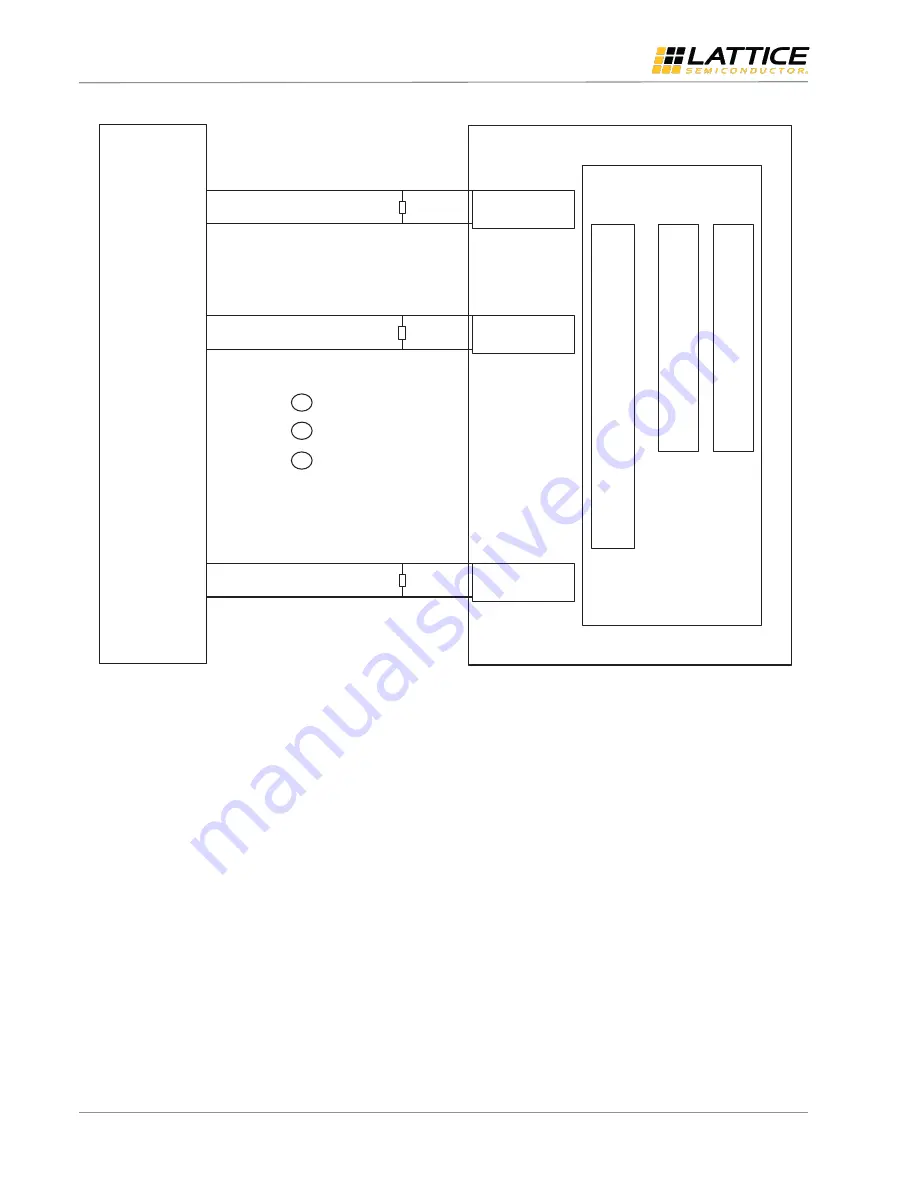

MIPI DPHY

TX Device

LATTICE FPGA

DATA3_P

DATA3_N

D3_p

D3_n

100 Ω

L

V

DS25

DPHY RX Module

I/

O

C

o

n

tro

lle

r

iD

D

R

x4

A

lig

n

e

r

L

V

DS25

LVDS25

DATA0_P

DATA0_N

D0_p

D0_n

100 Ω

CLOCK_P

CLOCK_N

DCK_p

DCK_n

100 Ω

Figure 3.2. Unidirectional Receive HS Mode Only Implementation