MIPI D-PHY Bandwidth Matrix Table

User Guide

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-UG-02041-1.1

25

7.3.

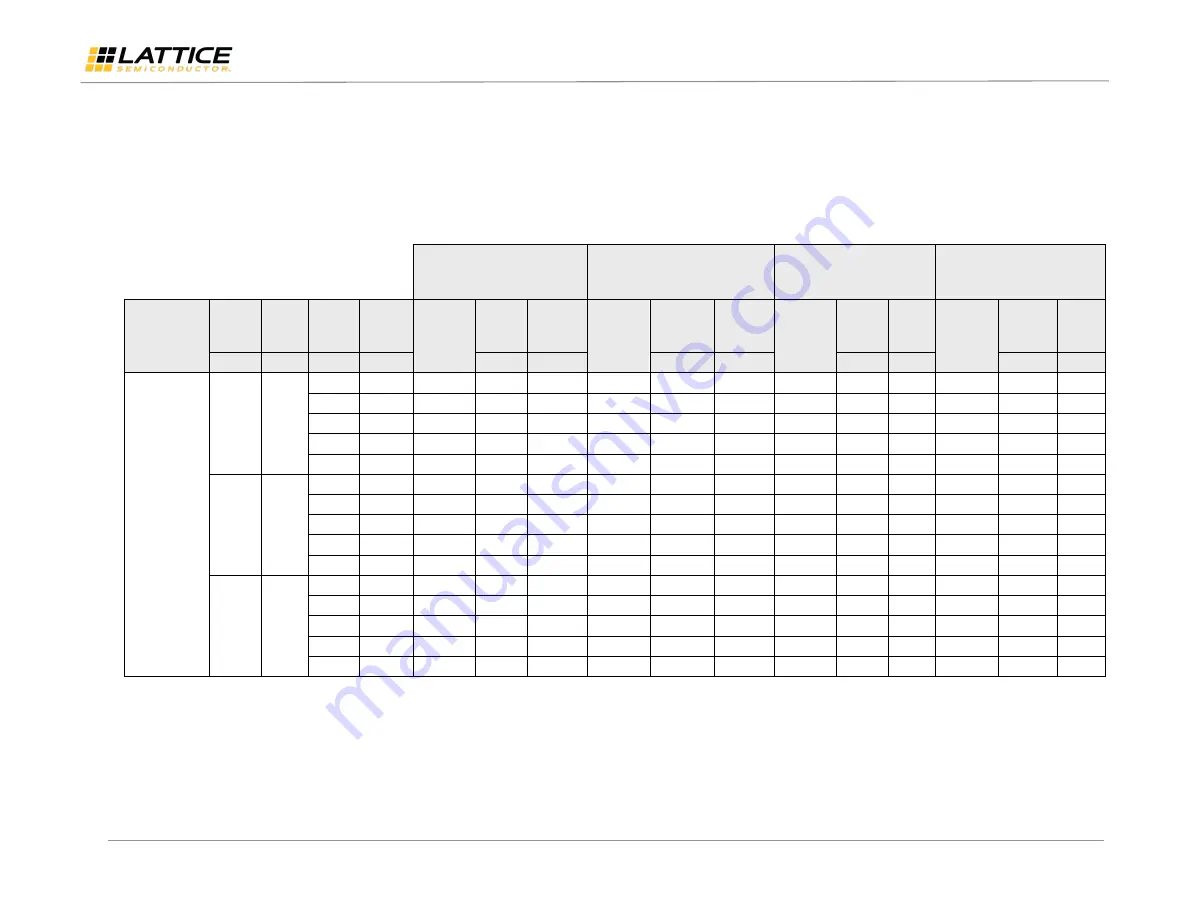

MIPI D-PHY Lane Number Selection Matrix Table

lists the selection of MIPI D-PHY Lane number and Line rate versus the Total Data Rate required by each video format. For clarity, this Matrix table only chooses

three common resolutions and the major color depths as examples. The lane number and line rate for other video formats can be calculated using the equations listed in

Bandwidth and Data Rate section.

Table 7.3. MIPI D-PHY Interface Lane Number and Line Rate Selection Example Matrix Table

MachXO2 and MachXO3L

(523 Mbps for RX and 728

Mbps for TX I/O)

LatticeECP3 (467 Mbps for RX

and 698 Mbps for TX I/O)

ECP5/ECP5-5G (467 Mbps

for RX and 820 Mbps for

TX I/O)

CrossLink (898 Mbps for RX

and 1250 Mbps for TX I/O)

Resolution

Frame

Rate

Pixel

Clock

Color

Depth

Total

Data

Rate

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Hz

MHz

Bits

Mbps

Mbps

MHz

Mbps

MHz

Mbps

MHz

Mbps

MHz

HD

1280x720p

(1650x750)

60

74.25

8

594

2

297

148.5

2

297

148.5

2

297

148.5

1

594

297

10

742.5

2

371

185.6

2

371

185.6

2

371

185.6

1

742.5

371

16

1188

4

297

148.5

4

297

148.5

4

297

148.5

2

594

297

18

1336.5

4

334

167

4

334

167

4

334

167

2

668

334

24

1782

4

445.5

223

4

445.5

223

4

445.5

223

2

891

445.5

120

148.5

8

1188

4

297

148.5

4

297

148.5

4

297

148.5

2

594

297

10

1485

4

371

185.6

4

371

185.6

4

371

185.6

2

742.5

371

16

2376

—

—

—

—

—

—

—

—

—

—

—

—

18

2673

—

—

—

—

—

—

—

—

—

—

—

—

24

3564

—

—

—

—

—

—

—

—

—

—

—

—

240

297

8

2376

—

—

—

—

—

—

—

—

—

4

594

297

10

2970

—

—

—

—

—

—

—

—

—

4

742.5

371

16

4752

—

—

—

—

—

—

—

—

—

—

—

—

18

5346

—

—

—

—

—

—

—

—

—

—

—

—

24

7128

—

—

—

—

—

—

—

—

—

—

—

—