Chapter 8: ENC/ENS/ENX-6801/M Encoder Modules and Accessories

User-Controlled Parameters

120

6800/7000 Series - Audio and Video Multi/Demultiplexing Products Installation and Operation Manual

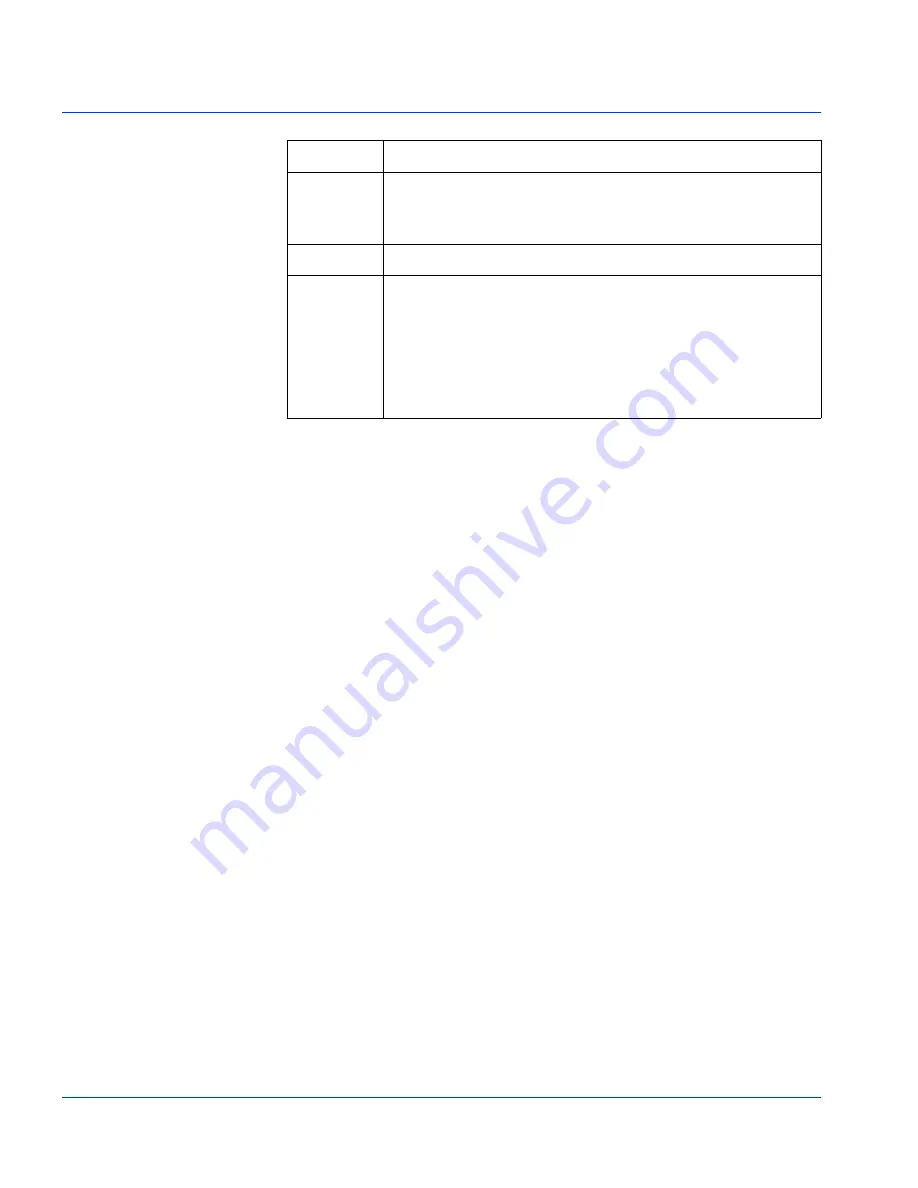

Delay Mode

In

Line

Delay

mode, the clock used to input to the memory buffer is

derived from the input signal. The clock used to output from the

memory buffer is also derived from the input signal. In this mode,

high-frequency jitter is removed at the input reclocking circuit, but

low-frequency jitter will pass right through the entire unit.

Line Store

In

Line Store

(i.e. line synchronizer) mode, the clock used to input to the

memory buffer is derived from the input signal. The clock used to

output from the memory buffer is derived from the input genlock signal.

In this mode, high-frequency jitter is removed at the input reclocking

circuit, and the low-frequency jitter is removed through the frame

buffer.

Input Signal

The modules are shipped in line

Delay

mode because the timing

relationships within the system are not known. If the input signal is not

advanced less than one line in time from the destination, the line

synchronizer in the encoder cannot provide the correct picture position.

Output Signal

The output signal will either “slip” a line up or down depending on

whether the signal is arriving at the destination early or late.

*5

Controls fine phase for ENC/ENX-6801. For fine phase control

of ENS-6801, use potentiometer on front of plug-in

submodule.

*6

Controls are disabled for PAL-M standard.

*7

• Increase refers to the SCH phase adjustment by 90°

increments from 0° to 270°.

• Decrease adjust the SCH phase in the opposite direction:

both of these adjustments are for PAL signals.

• NTSC signals will change to 0° or 180° phasing when

selecting either increase or decrease.

Function Description