Copyright © 2009 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

- 20 -

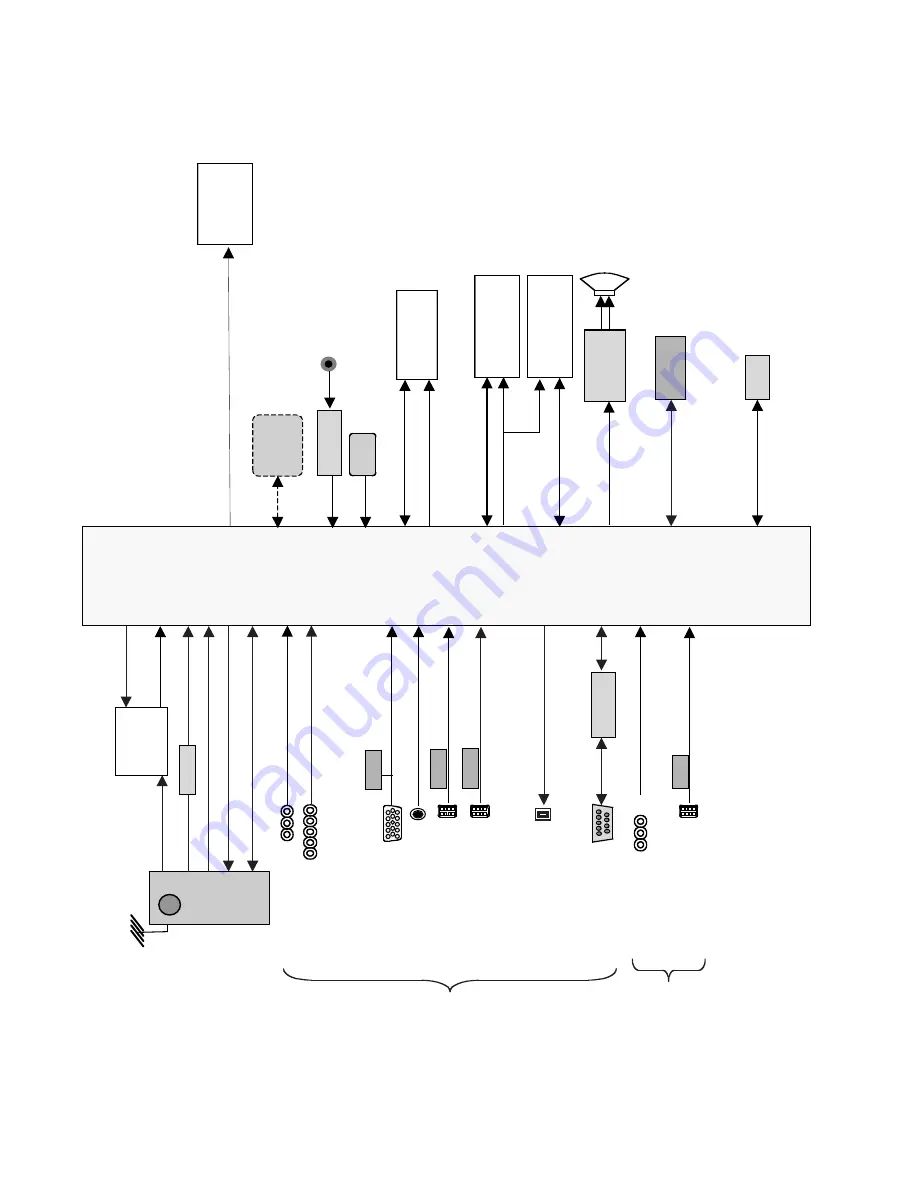

BLOCK DIAGRAM

D-sub RGB

HDMI 1

Side AV

CVBS, L/R

DDR2 (512Mbit)

Qimonda /

Hynix

NAND Flash

(256Mb)

Digital Audio (Optic)

Digital AMP

NTP3100L

RS-232C (Ctrl./SVC)

I2S

EEPROM

512Kb

RGB/H/V

Half-NIM Tuner

DDR_Data[0:15], DQS, DM...

Addr.[ ], ctrl. data

MAX3232

Saturn5

(ATSC

US)

MPEG2

Linux

Scaler

Data [0...7]

IF +/-

SIF

TU_CVBS

Reset / IF_AGC...

SDA/SCL_5V

JTAG

CLK,TDI,TDO,MS,RST

Addr[0...1], CS...

Audio L/R

Audio L/R (for RGB)

HDMI 2

SPDIF

RX/TX

RX/TX

JACK PACK

at REAR

JACK PACK

at SIDE

SCL, SDA_3.3V

TR Buffer

VSB

Demod

.

LGDT3305

X-tal

Reset Switch

Reset IC

12MHz

TS In[0...7

]

TS_clk, SOP, Val

EEPROM

Data[16:31]

DDR2 (512Mbit)

Qimonda /

Hynix

AV

Component 1

Y Pb Pr, L/R

CVBS, Y/C, L/R

SCL, SDA_3.3V

Bluetooth

Dongle

(Option)

DP/DM

LCD Module

(FHD,HD)

LVDS

EEPROM

EEPROM

HDMI 3

EEPROM