Copyright ⓒ 2009 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

MAIN

MAIN

Board

Board

Jack

Jack

Board

Board

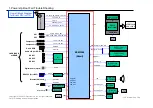

D1.2V, D2.5V, +3.3V, +5.0V_ST

SCL0_3.3V, SDA0_3.3V, DDC_SCL, DDC_SDA

CVBS, SIF, AV, RGB ,COMPONENT, R/L,

TU_SCLK, TU_DATA, TU_SYNK’’..

< Signal Interface >

SPDIF , EDID_WP ….

Block Diagram

Summary of Contents for 47SL90QD

Page 32: ......