31

256 241

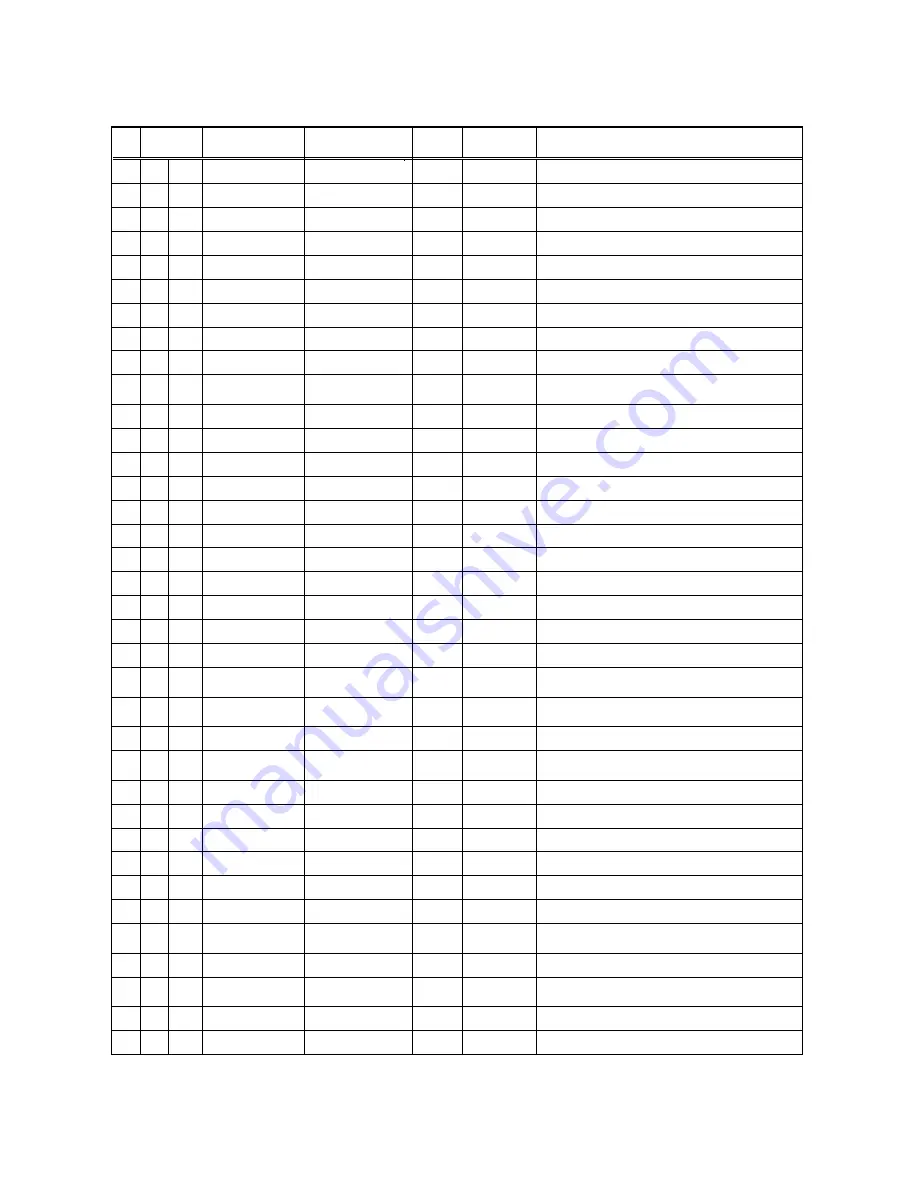

Pin

name

System controller

external connection

I/O

Destination

Description

71 65 - V

SS

GND

-

V

SS

72 66 C5 MDQ8

I/O

DRAM SDRAM

data

73 67 B5 MDQML

O

DRAM SDRAM

data

74 68 E7 MNWE

O

DRAM SDRAM

control

75 69 A4 MDQMU

O

DRAM SDRAM

data

76 70 C6 MNCAS

O

DRAM SDRAM

control

77 71 A5 MCLKI

I

DRAM SDRAM

clock

input

78 72 - V

SS

GND

-

V

SS

79 73 C7 MCLK

O

DRAM SDRAM

control

80 74 - V

DD3

Power

supply

-

V

DD

(3.3 V)

81 75 A6 MNRAS

O

DRAM SDRAM

control

82 76 B6 MCKE

O

DRAM SDRAM

control

83 77 A7 MBA0

O

DRAM

SDRAM

control

84 78 B7 MA11

O

DRAM

SDRAM

address

85 79 A8 MBA1

O

DRAM

SDRAM

control

86 80 B8 MA9

O

DRAM

SDRAM

address

87 81 C8 MA10

O

DRAM

SDRAM

address

88 82 D8 MA8

O

DRAM

SDRAM

address

89 83 A9 MA0

O

DRAM

SDRAM

address

90 84 B9 MA7

O

DRAM

SDRAM

address

91 85 - V

SS

GND

-

V

SS

92 86 - V

DD15

Power

supply

-

V

DD

(1.5 V)

93 NC NC _DRAMV

DD15

Power

supply

-

DRAM Power supply (1.5 V)

94 NC NC _DRAMV

SS

GND

-

V

SS

for DRAM use

95 87 - V

DD3

Power

supply

-

V

DD

(3.3 V)

96 88 A10 MA1

O

DRAM SDRAM

address

97 89 E9 MA6

O

DRAM

SDRAM

address

98 90 A11 MA2

O

DRAM

SDRAM

address

99 91 D10 MA5

O

DRAM

SDRAM

address

100 92 A12 MA3

O

DRAM

SDRAM

address

101 93 B10 MA4

O

DRAM

SDRAM

address

102 94 A13

WGATE/P14(PAN

ICIN) I/O

EFEP

Write

assert/General-purpose

port

103 95 C10 NWGATE/P15

I/O

LDD

Write assert inverted signal/General-purpose port

104 96 B11 HFSW/P16 I/O

LDD

High-frequency superimposition circuit

control/General-purpose port

105 97

E10 SH7/LDCNT3

O

LDD

General-purpose S/H 7/LD driver control

106 98 - V

SS

GND

-

V

SS