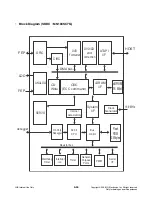

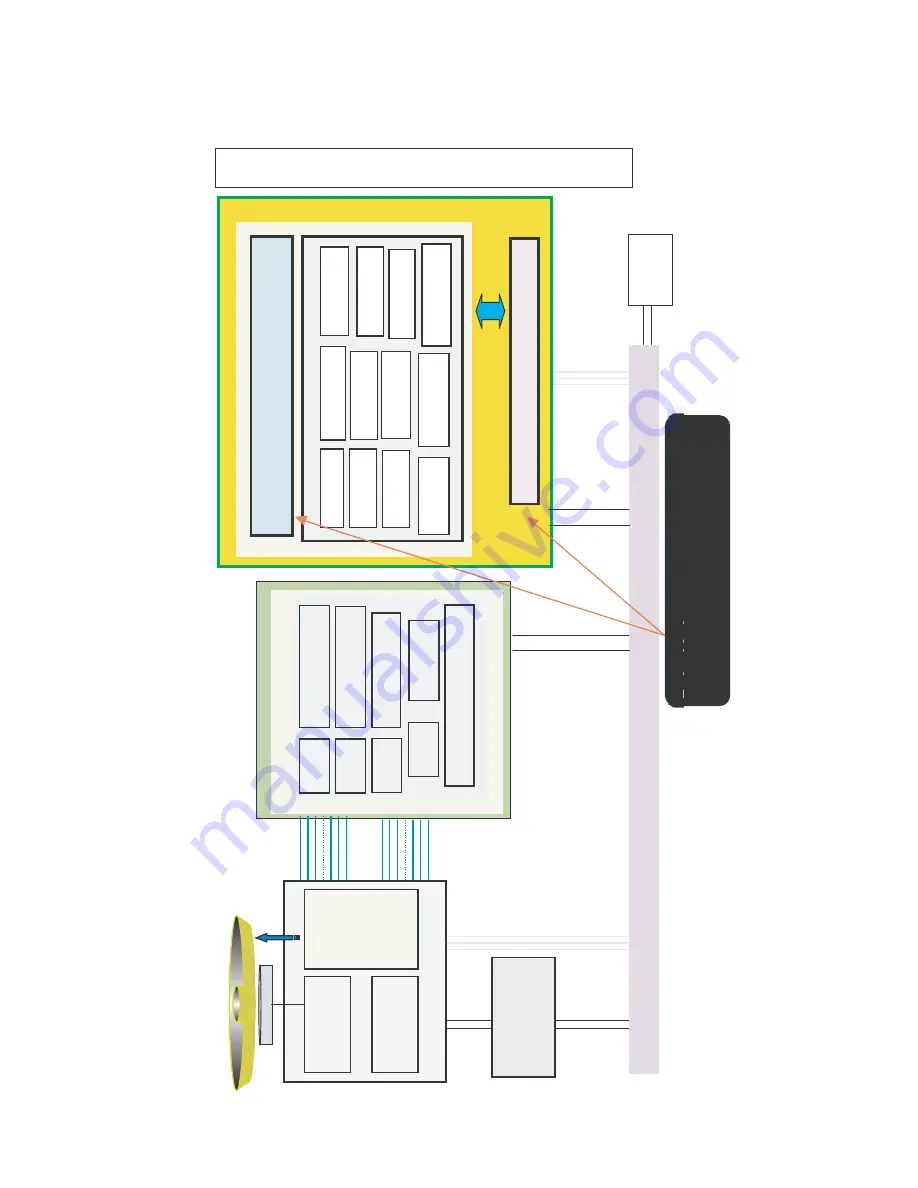

BLOCK DIAGRAM

4-51

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

LPP

RF-EQ,AGC

+R/RW WBL

Sp

indl

e

m

o

to

r

Sl

e

d

m

o

to

r

Op

ti

cal

pi

c

k

-u

p

Re

gul

a

tor

3.

3v

/1

.20v

1ch

ip

S

e

n

s

or

-l

e

s

s

Mo

to

r d

ri

v

e

(R

oh

m

BD

7776)

Ho

s

t

Em

b

e

dde

d

Fl

a

s

h

R

O

M

& S

D

R

A

M

16M

-e

D

R

AM

DRC

SERVO

OD

C

ECC/CIRC

ATAPI

32b CPU

DEC

ENC

CD-ENC

16Mbit Flash Memory

16x WTST

RAM 16x

RAM 16x

F

EP A

N22117

Servo M

T

X

WBL

OPC

TCTI

DPD

SYSCON

LP

C(

LAS

E

R

P

O

W

E

R)

SODC MN103SC7G

Se

ri

a

l