3-34

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

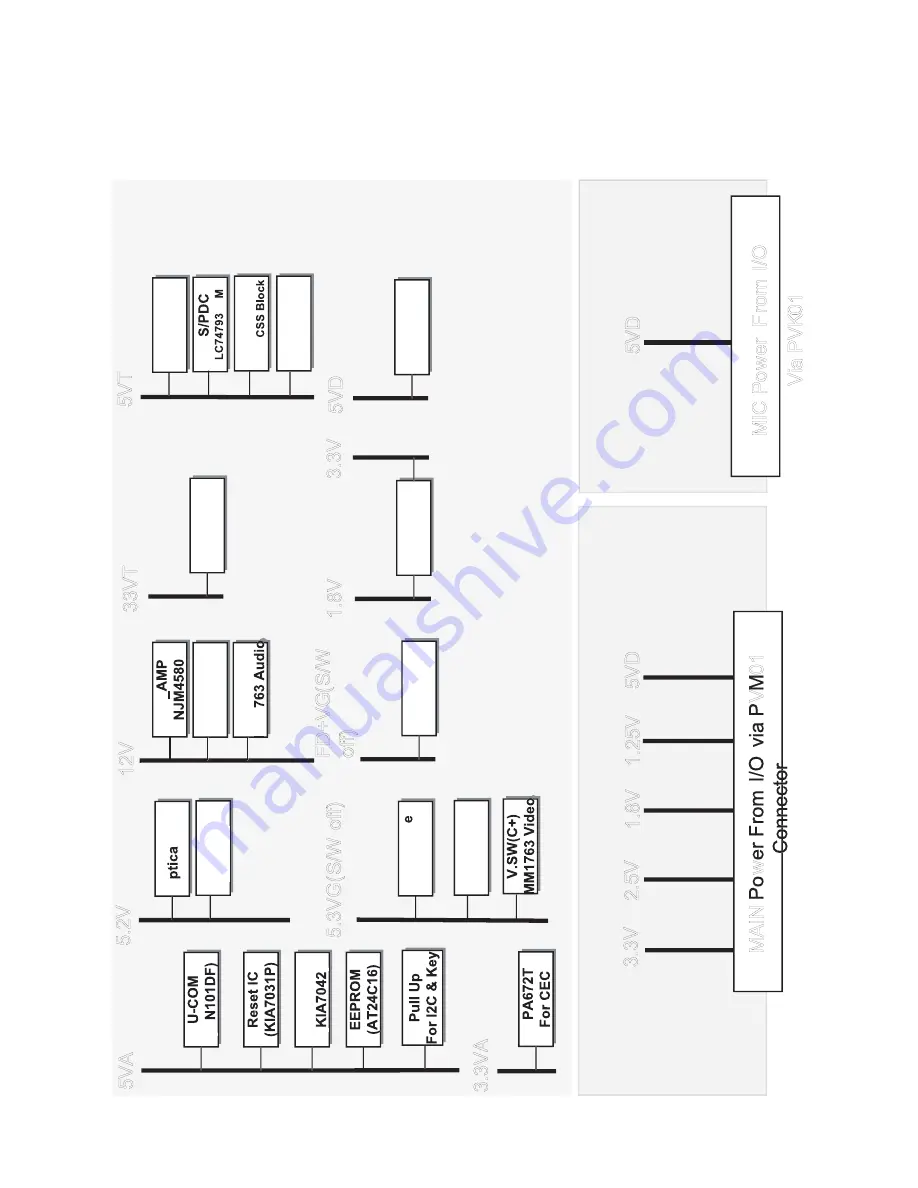

4. POWER I/O BLOCK DIAGRAM

5VA

P

WR Fail

((

))

((M

5.2V

O

l Jack

12V

O

P

5VT

33VT

T

uner

T

uner

FLD Driv

P

T6315

FD+VG

(S/W

off)

D

ig

itron

5.3VG

(S/W

off)

1.8V

SA

A

713

8

3.3V

VP

NJ

T

UNER

B

oost

er

U

-CO

M

For

A

3.3VA

U

M

od Buffer

6dB AMP

M

M1510

V

.SW

(C+

)

MMM1M

P

ull UP

For Si

g

n

g

al

3.3V

2.5V

1.8V

1.25V

5VD

M

A

IN

w

V

0

1

PC

M

17

80

A

udio DAC

5VD

5VD

M

IC

P

o

w

er F

rom

I/O

Vi

a PVK

0

KK

0

1