3-35

Copyright © 2008 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

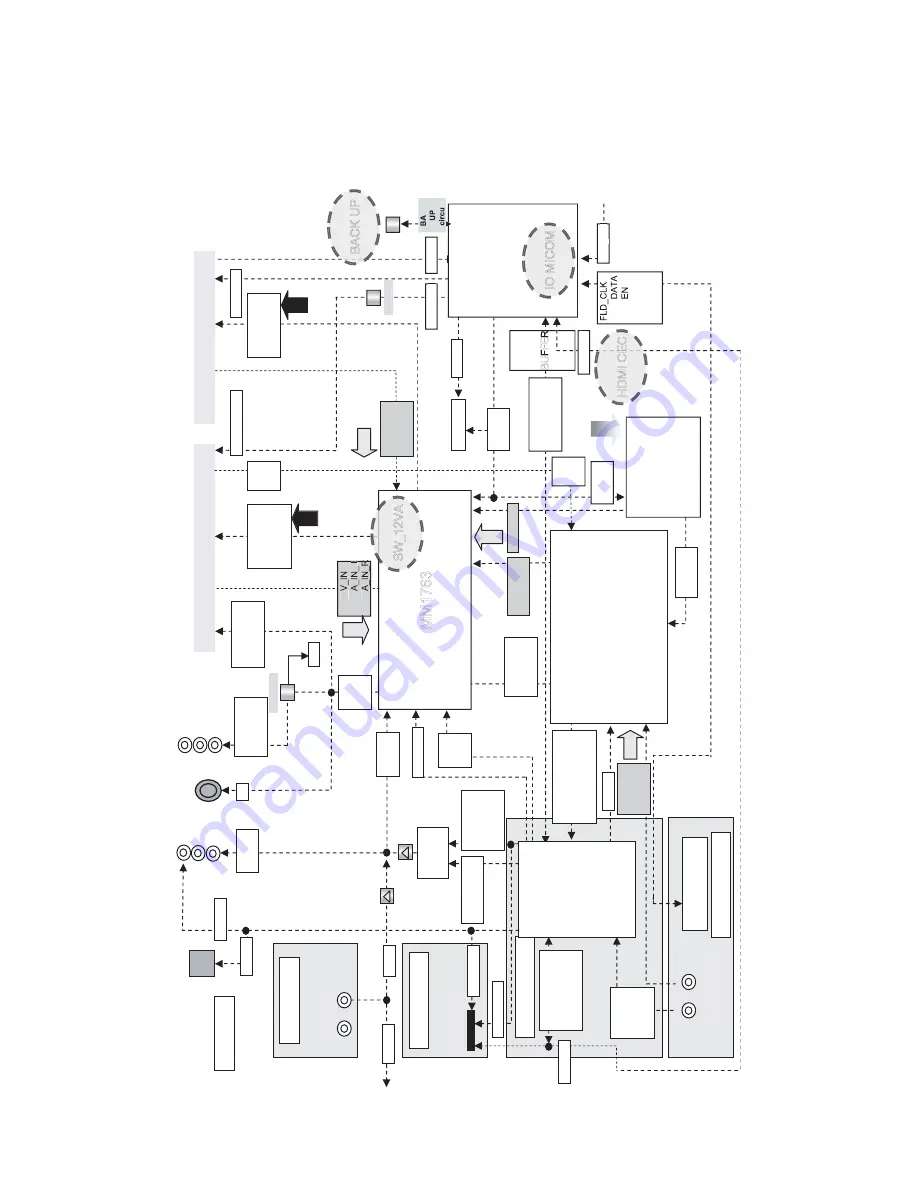

5. A/V BLOCK DIAGRAM

Pr_OU

T

Y_OUT

Pb_OU

T

A_

L_OUT

A_

R

_OUT

CO

A

X

IA

L

FRONTF

R

O

N

T

JA

CK C

K

MAIN BOARD

I/OI/O

B B

O

A

R

D

AOUT_SCLK

AOUT_F

SY

NC

AOUT_

D

0

AOUT_MCLK

EU

1_

EU

1_

LL

EU

1_

CVBS

_O

UT

EU

1_

V_OU

T

EU

1_

A_OU

T_L

EU

1_

A_OU

T_

R

SC

A

R

T_

H

EU

2_

V_OU

T

EU

2_

A_OU

T_L

EU

2_

A_OU

T_

R

A_OUT

_L

A_OUT

_R

EU2

_V_

IN

EU

2_

A_IN_

L

EU

2_

A_IN_

R

R

GB

_I

N

C+_D

ET_H

T

R circu

it

T

R

GB

_OU

TT

RGB_SEL_OUT

SW

_A

_OUT_

L

SW

_A

_OUT_

R

SW

_

V_OU

T

AI

N_MCL

K

OU

T

AI

N_F

S

Y

N

C,

AI

N

_SCLK

AI

N_D0, VIN[

2:

9]

V_INT, V_

CL

K

Y_

RCA_

O

U

T

Pb_

RCA

_O

U

T

Pr_R

C

A

_OUT

R_

SC

ART_OU

T

G_SC

A

R

T_OUT

B_

S

C

ART_

O

UT

TR c

ircu

it

Y,

P

b,

P

r

R,

G,

B

Y,

C

A_OUT

_L

A_OUT

_R

GND

MM1

76

SIF

SE

CA

M_A

M

Y,

P

b,

P

r

R,

G,

B

Y,

C

COAX

IAL

AUDIO

DAC

F_A_R

_I

N

F_A

_L_IN

F_

CVBS

_I

N

USB+,

US

B

-

USB_

5V

TPA+,

TPA-

TPB+,

TPB-

TU_R_A

_O

UT

TU_

L_A

_O

UT

Y,

C

OPTIC

A

L

TIMER BO

ARD

FLD

DRIVER

F

LD

_

F

LD

_

A

KE

Y

_RTN_

0

KE

Y_RTN_

N

1

RMC_I

N

IO MICO

M

SAA7138

SCART 1

SCART 2 (Decorder)

SCL

, SDA

HOST_

D

A

TA_

I

N

HOST_EN

A

MIM

IC

JAJ

A

CK C

K

MIC BOARD

MIC

_IN

MV3

BU

F

E

HO

ST

_D

A

T

A

_IN

H

OST

_D

AT

A

_OU

T

HO

ST

_EN

A

HDMIH

D

M

I JACK J

A

C

K

HDMI BOARD

HDMI

_C

EC

SPDI

F_OU

T

AOUT_MCLK

VO_D

[0:1

5]

VOU

T

_CLK

I2C_

SC

L,

I2C

_S

D

A

AD

938

9_INT

MIC

_D

E

T

T

UNER

I2C

_C

LK

I2C

_D

A

T

AAA

R_I

N

G_IN

B_

IN

R_I

N

G_IN

B_IN

M

IC

_D

E

TTT

TU_

V_OUT

MM1763

EEPROM

I2C

_C

LK

I2C

_D

A

T

A

JIG_EN

A

HDMI

C

EE

C

HDMI

_C

E

CCC

BACK UP

C

K

it

IO

M

IC

O

M

SW

_12VA

W