3. TECHNICAL BRIEF

- 41 -

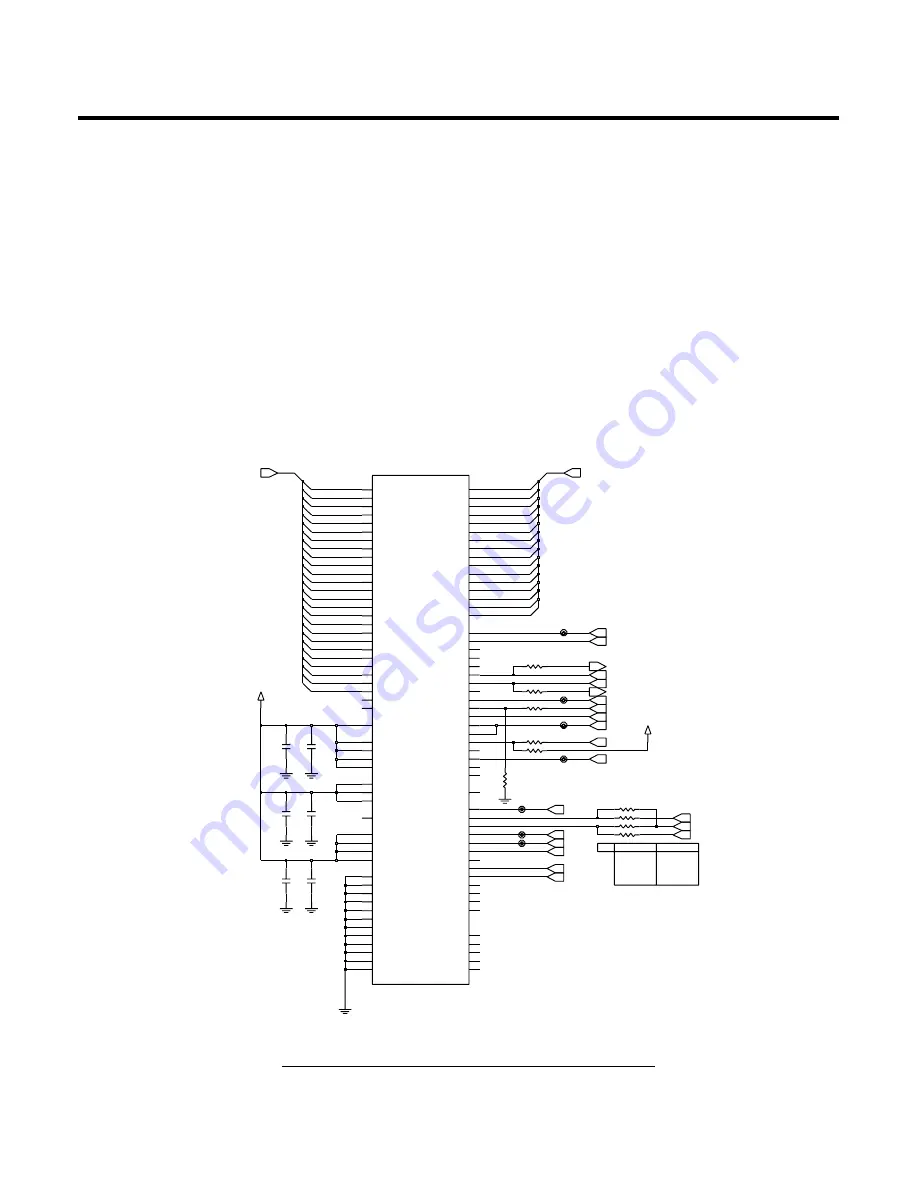

3.6. Memory

256Mbit Flash & 128Mbit SDRAM employed on KE820/KG99 with 16 bit parallel data bus thru

ADD(0)~ ADD(24). The 256Mbit Sibley Wireless Flash memory with LPSDRAM stacked device family

offers multiple high-performance solutions. The Sibley flash die is manufactured on 90 nm process

technology. It delivers 108 MHz synchronous burst and page-mode read rates with supports multi-

partitioning with Read-While-Write (RWW) or Read-While-Erase (RWE) dual operations. The

LPSDRAM is a high-performance volatile memory operating at speeds up to 104 MHz with

configurable burst lengths.

Open

Short

JP2

JP3

JP3

Short

Open

256M SDRAM

Open

JP1

128M SDRAM

JP2

Open

Short

JP0

JP0

JP1

Short

NA

R115

TP113

TP112

F1

_OE

H7

_S_CS1

F6

E2

_WE

VSS7

VSS8

K3

K4

VSS9

F2

_D1_CS

E3

_D2_CS

F3

_D_CAS

_D_CLK

H5

_D_RAS

F4

H6

_D_WE

_F1_CE

G3

G2

_F2_CE

H3

_F3_CE

_F4_CE_A27

E6

D5

_F_ADV

G7

_F_RST

_F_WP1

E1

_F_WP2

RFU

H2

S_CS2

S_VCC

D2

VCCQ1

J2

J3

VCCQ2

J7

VCCQ3

J8

VCCQ4

C2

VSS1

K6

VSS10

VSS11

K7

K8

VSS12

VSS2

C3

C4

VSS3

C6

VSS4

VSS5

C7

C8

VSS6

K2

M3

M7

D_UDQS

D_VCC1

C5

D3

D_VCC2

D7

D_VCC3

F_CLK

K5

B6

F_DPD

F_VCC1

D4

F_VCC2

D6

F_VCC3

J4

F_VCC4

J6

J1

F_VPP

J9

F_WAIT

D8

N_ALE

E5

N_CLE

N_RY__BY

H1

G1

DQ4

L3

DQ5

L4

DQ6

L5

DQ7

DQ8

M5

DQ9

L6

A1

DU1

A9

DU2

DU3

M1

M9

DU4

D_BA0

G4

H4

D_BA1

G6

D_CKE

J5

D_CLK

D_DM0__S_LB

H9

D_DM1__S_UB

H8

D_LDQS

A2

B3

A5

A6

A3

A7

A4

G8

A8

F8

A9

M2

DQ0

L1

DQ1

M6

DQ10

L7

DQ11

DQ12

L8

DQ13

K9

L9

DQ14

M8

DQ15

DQ2

K1

DQ3

L2

M4

E9

A14

D9

C9

A15

A16

B9

A17

B4

A18

B5

A5

A19

A2

B1

A20

F7

A21

E7

A22

B7

A6

A23

A7

A24

A25

A8

B8

A26

B2

A3

A4

U101

PF38F5060M0Y0B0

A0

D1

C1

A1

E8

A10

G9

A11

A12

F9

A13

22

R112

NA

R446

R445

NA

0.1u

C126

C125

0.1u

TP209

R114

10K

R118

100K

R444

0

22

R113

1V8_MEM

R443

0

0.1u

C127

C129

0.1u

0.1u

0.1u

C130

C128

TP105

TP107

TP109

TP108

R117

0

1V8_MEM

_ADV

_BC0

_BC1

A(14)

A(13)

A(12)

_FLASH1_CS

_RD

BFCLKI

_WP

SDCLKI

_RESET

A(0:24)

D(0:15)

D(13)

D(14)

D(15)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

CKE

SDCLKO

BFCLKO

F_DPD

_WAIT

_RAM_CS

_CAS

_RAS

_WR

A(21)

A(22)

A(23)

A(24)

A(3)

A(4)

A(5)

A(6)

A(7)

A(8)

A(9)

D(0)

D(1)

D(10)

D(11)

D(12)

A(0)

A(1)

A(10)

A(11)

A(12)

A(13)

A(14)

A(15)

A(16)

A(17)

A(18)

A(19)

A(2)

A(20)

Figure 11 Flash memory & SDRAM MCP circuit diagram

Summary of Contents for KE820

Page 1: ...Service Manual Model KE820 Service Manual KE820 Date August 2006 Issue 1 0 ...

Page 3: ... 4 ...

Page 5: ... 6 ...

Page 46: ...3 TECHNICAL BRIEF 47 Figure 18 EN SET port control method ...

Page 69: ...4 PCB layout 70 Figure 45 Main PCB bottom Figure 46 Main PCB bottom placement ...

Page 70: ...4 PCB layout 71 Figure 47 Sub PCB top Figure 48 Sub PCB top placement ...

Page 71: ...4 PCB layout 72 Figure 49 Sub PCB bottom Figure 50 Sub PCB bottom placement ...

Page 114: ...6 Download S W upgrade 115 6 2 Download program user guide ...

Page 115: ... 116 6 Download S W upgrade ...

Page 116: ... 117 6 Download S W upgrade ...

Page 117: ... 118 6 Download S W upgrade ...

Page 124: ... 125 8 PCB LAYOUT ...

Page 125: ... 126 8 PCB LAYOUT ...

Page 126: ... 127 8 PCB LAYOUT ...

Page 127: ... 128 8 PCB LAYOUT ...

Page 141: ... 142 ...

Page 161: ...Note ...

Page 162: ...Note ...