5. BLOCK DIAGRAM

- 210 -

Copyright © 2013 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

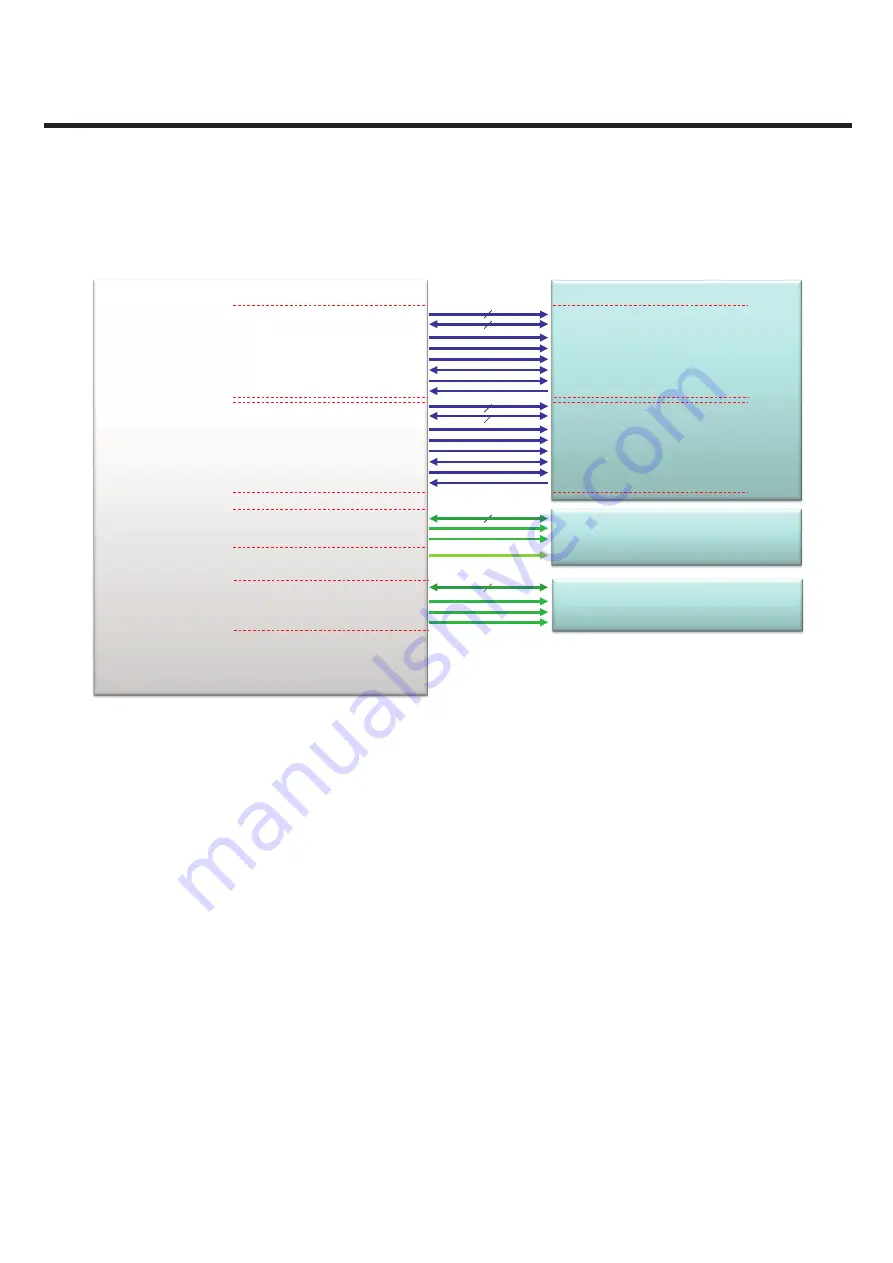

[D802] Memory I/F

Main Chipset

(MSM8974)

DQ_0~31

DDR3 800MHz

DQ0~31_a

SDC1_DATA_0~7

eMMC 4.5

DATA0~7

CMD

CLK

SDC1_CMD

SDC1_CLK

CA_0~9

CA0~9_a

RESOUT_N

RESOUT_N

EBI0

EBI1

SDC1

Connectivity

SDC2_DATA_0~2

WL_CMD_DATA0~2

WL_CMD_SET

WL_CMD_CLK

SDC2_CMD

SDC2_CLK

SDC2

BT_SSBI

SDC2_DATA_3

DCLK / DCLKB

CK / CK_N_a

CKE_0~1

CKE0~1_a

CS0~1_N

DQS_0~3 / DQS_0B~3B

DM_0~3

ZQ

CS0~1_N_a

DQS0~3_b / DQS0~3_N_b

DM0~3_a

ZQ_a

DQ_0~31

DQ0~31_b

CA_0~9

CA0~9_b

DCLK / DCLKB

CK / CK_N_b

CKE_0~1

CKE0~1_a

CS0~1_N

DQS_0~3 / DQS_0B~3B

DM_0~3

ZQ

CS0~1_N_b

DQS0~3_b / DQS0~3_N_b

DM0~3_b

ZQ_b

CH_A

CH_B

10

32

10

32

8

3

5. Memory I/F