3-33

3-3. PIN DESCRIPTION

Pin

Description

A0-A19

20 Addresses

DQ0-DQ14

15 Data Inputs/Outputs

DQ15/A-1

DQ15 (Data Input/Output, Word Mode)

A-1 (LSB Address Input, Byte Mode)

CE#

Chip Enable

OE#

Output Enable

WE#

Write Enable

RESET#

Hardware Reset Pin, Active Low

BYTE#

Selects 8-bit or 16-bit mode

RY/BY#

Ready/Busy Output (N/A SO 044)

Vcc

3.0 volt-only single power supply

(see Product Selector Guide for speed options and voltage supply tolerances)

Vss

Device Ground

NC

Pin Not Connected Internally

Summary of Contents for MBD-D102X

Page 7: ...1 6 MEMO ...

Page 10: ...2 5 3 SPEAKER SECTION MBS D102V 750 751 752 754 755 757 A70A 758 A70 757A 759 756 753 ...

Page 35: ...3 24 4 FOCUS WAVEFORM 1 FDO 2 F 3 F INSERT CD INSERT DVD 1 FDO 2 F 3 F ...

Page 37: ...3 26 7 TRACKING SIGNAL 1 Tro 2 Tr 3 Tr 8 RF WAVEFORM ...

Page 38: ...3 27 9 DISK TYPE JUGEMENT WAVEFORM 1 F 2 FDO 3 SVRRF DVD CD ...

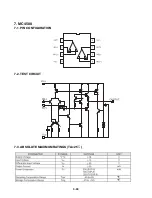

Page 50: ...3 39 7 MC4580 7 1 PIN CONFIGURATION 7 2 TEST CIRCUIT 7 3 ABSOLUTE MAXIMUM RATINGS TA 25 ...

Page 60: ...3 49 3 50 WIRING DIAGRAM ...

Page 62: ...3 53 3 54 2 MAIN FRONT BLOCK DIAGRAM ...

Page 64: ...3 57 3 58 2 MAIN INTERFACE PWM SCHEMATIC DIAGRAM ...

Page 65: ...3 59 3 60 3 MPEG SCHEMATIC DIAGRAM ...

Page 66: ...3 61 3 62 4 SERVO SCHEMATIC DIAGRAM ...

Page 67: ...3 63 3 64 5 INTERFACE SCHEMATIC DIAGRAM ...

Page 68: ...3 65 3 66 6 FRONT SCHEMATIC DIAGRAM ...

Page 69: ...3 67 3 68 7 FRONT MIC SCHEMATIC DIAGRAM ...

Page 70: ...3 69 3 70 8 IPOD 1 SCHEMATIC DIAGRAM OPTION ...

Page 71: ...3 71 3 72 9 IPOD 2 SCHEMATIC DIAGRAM OPTION ...

Page 72: ...3 73 3 74 10 2 CHANNEL AMP SCHEMATIC DIAGRAM ...

Page 73: ...3 75 3 76 11 BLUTHOOTH MODULE SCHEMATIC DIAGRAM OPTION ...

Page 75: ...3 79 3 80 1 MAIN P C BOARD TOP VIEW PRINTED CIRCUIT BOARD DIAGRAMS ...

Page 76: ...3 81 3 82 MAIN P C BOARD BOTTOM VIEW ...

Page 77: ...3 83 3 84 2 FRONT P C BOARD TOP VIEW BOTTOM VIEW ...

Page 78: ...3 85 3 86 3 SMPS P C BOARD TOP VIEW BOTTOM VIEW ...