3-35

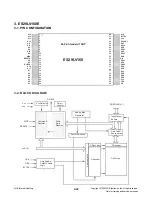

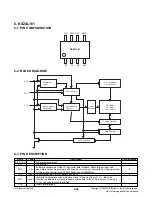

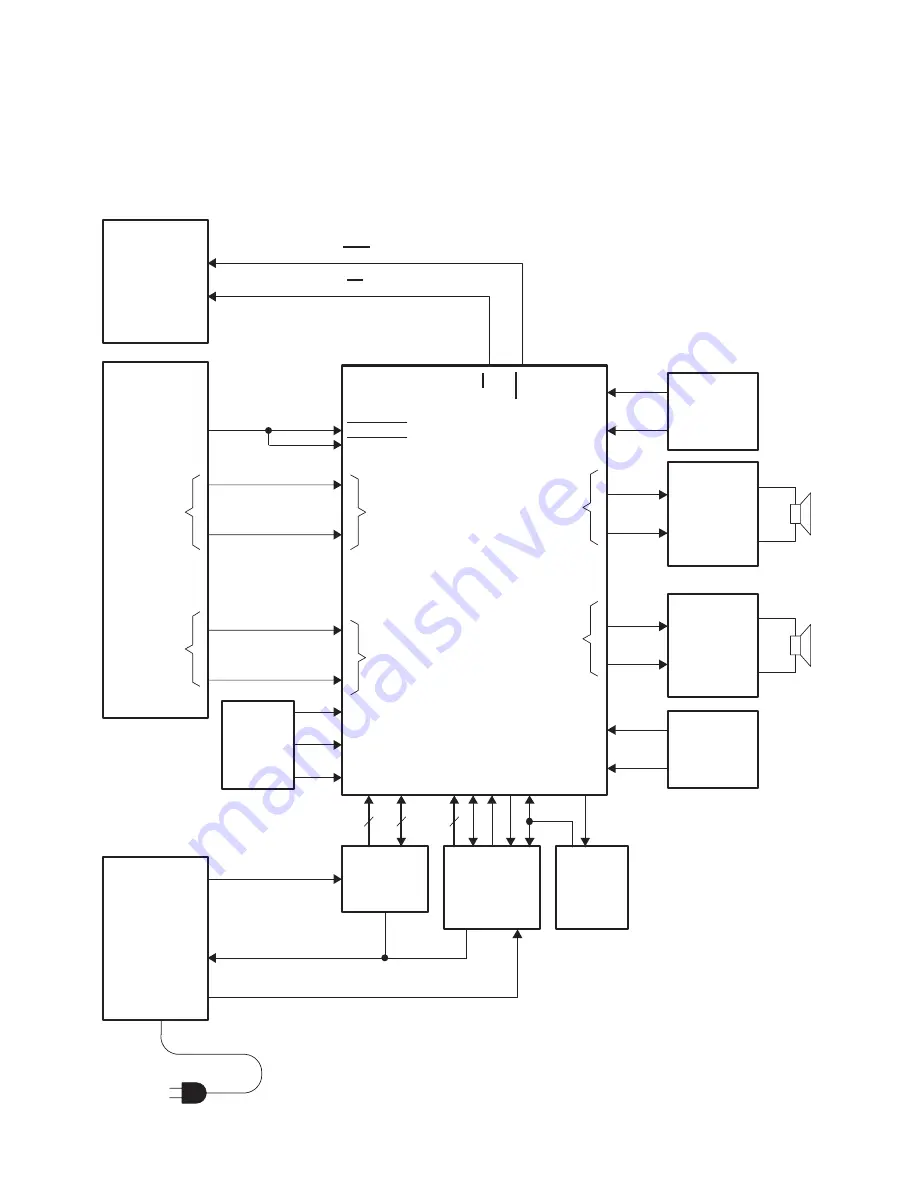

4-2. SYSTEM BLOCK DIAGRAM

2nd -Order L-C

Output Filter

for Each

Half-Bridge

Bootstrap

Capacitors

2-Channel

H-Bridge

BTL Mode

System

Microcontroller

OUT_A

OUT_B

OUT_C

OUT_D

BST_A

BST_B

BST_C

BST_D

RESET_AB

RESET_CD

System

Power

Supply

Hardwire

Mode

Control

PVDD

GVDD (12 V)/VDD (12 V)

GND

Hardwire

OC Limit

M1

M3

PVDD

Power

Supply

Decoupling

35 V

12 V

GND

VAC

PWM_A

PWM_C

PWM_D

PWM_B

VALID

M2

Left-

Channel

Output

Right-

Channel

Output

Input

H-Bridge 1

Input

H-Bridge 2

GVDD

VDD

VREG

Power Supply

Decoupling

4

PVDD_A, B, C, D

GND_A, B, C, D

GVDD_A, B, C, D

4

4

VDD

GND

VREG

AGND

OC_ADJ

Bootstrap

Capacitors

2nd -Order L-C

Output Filter

for Each

Half-Bridge

SD

OTW

Output

H-Bridge 2

Output

H-Bridge 1

OTW

SD

TAS5508

Copyright © 2007 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only