4

dc1925af

DEMO MANUAL DC1925A

DC1925A SETUP

Data Collection

For SINAD, THD or SNR testing a low noise, low distortion

differential output sine generator such as the Stanford

Research DS360 should be used. A low jitter RF oscillator

such as the Rohde & Schwarz SMB100A or DC1216A-C

is used as the clock source.

This demo board is tested in house by attempting to

duplicate the FFT plot shown in the typical performance

characteristics of the LTC2378-20 data sheet. This involves

using an 80MHz clock source, along with a differential

output sinusoidal generator at a frequency of 2.0kHz.

The input signal level is approximately –1dBfs. The input

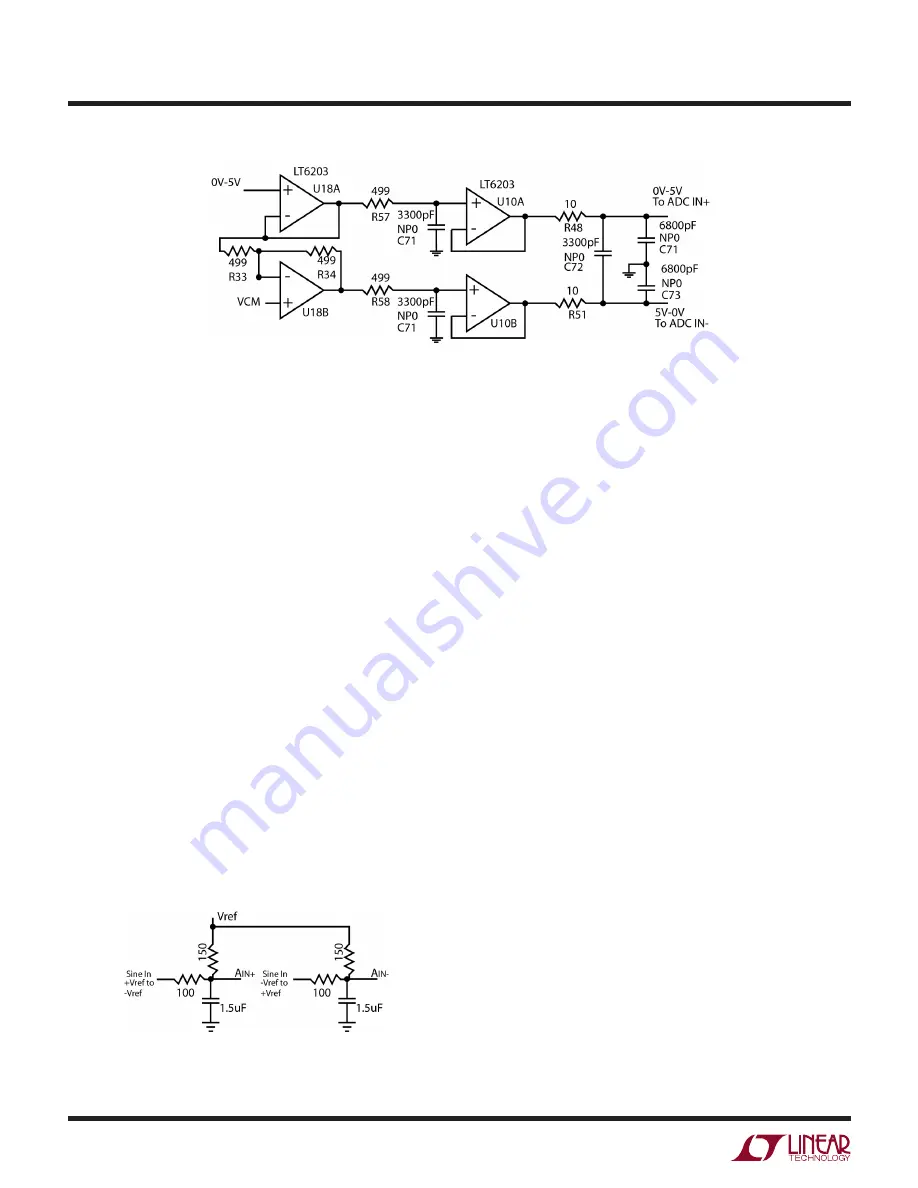

is level shifted and filtered with the circuit shown in Fig-

ure 4. A typical FFT obtained with DC1925A is shown in

Figure 5. Note that to calculate the real SNR, the signal level

(F1 amplitude = –0.998dB) has to be added back to the

SNR that PScope displays. With the example shown in Fig-

ure 5 this means that the actual SNR would be 103.668dB

instead of the 102.67dB that PScope displays. Taking the

RMS sum of the recalculated SNR and the THD yields a

SINAD of 103.62dB which is fairly close to the typical

number for this ADC.

Figure 3. Single-Ended-to-Differential Driver

There are a number of scenarios that can produce mislead-

ing results when evaluating an ADC. One that is common

is feeding the converter with a frequency, that is a sub-

multiple of the sample rate, and which will only exercise

a small subset of the possible output codes. The proper

method is to pick an M/N frequency for the input sine wave

frequency. N is the number of samples in the FFT. M is

a prime number between one and N/2. Multiply M/N by

the sample rate to obtain the input sine wave frequency.

Another scenario that can yield poor results is if you do

not have a sine generator capable of ppm frequency ac-

curacy or if it cannot be locked to the clock frequency. You

can use an FFT with windowing to reduce the “leakage” or

spreading of the fundamental, to get a close approxima-

tion of the ADC performance. If windowing is required,

the Blackman-Harris 92dB window is recommended. If an

amplifier or clock source with poor phase noise is used,

windowing will not improve the SNR.

Layout

As with any high performance ADC, this part is sensitive

to layout. The area immediately surrounding the ADC on

the DC1925A should be used as a guideline for placement,

and routing of the various components associated with the

ADC. Here are some things to remember when laying out a

board for the LTC2378-20. A ground plane is necessary to

obtain maximum performance. Keep bypass capacitors as

close to supply pins as possible. Use low impedance returns

directly to the ground plane for each bypass capacitor.

Use of a symmetrical layout around the analog inputs will

minimize the effects of parasitic elements. Shield analog

Figure 4. Differential Level Shifter