4-14

Register Descriptions

4.2.7 Registers 21 and 22

REF_DUR

Duration Between NCO Step Updates

R/W [15:0]

This parameter determines the duration between the

NCO step updates in multiples of the sync length. These

are NCO-related register fields; they are used only in PLL

Mode 2. Bit 0 resets to 1; all other bits reset to 0.

4.2.8 Registers 23 and 24

PROB_DUR

Byte Clock Duration

R/W [15:0]

This parameter determines the duration for the byte clock

measurement in units of 256 ICLK cycles. These are

NCO-related register fields; they are used only in PLL

Mode 2. The reset value is 0.

4.2.9 Register 25

N_PCLK

PCLK Cycles

R/W [7:0], R

This is the number of PCLK cycles during one ICLK byte

clock. The value in this register is valid only if the

MEASUREMENT_DONE bit in the NCO control register

is set. These are NCO-related register fields; they are

used only in PLL Mode 2. The reset value is 0.

4.2.10 Registers 26, 27, and 28

NM_COUNT

R [23:0]

This value is the number of CLK cycles found within the

duration of the (n

−

1) PCLK cycles. The value in this

15

0

REF_DUR

15

0

PROB_DUR

7

0

N_PCLK

23

0

NM_COUNT

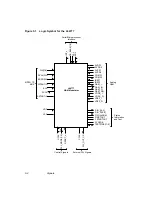

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......