363-206-295

Transmission and Synchronization Interfaces

5-10

Issue 1

December 1997

Synchronization Interfaces

5

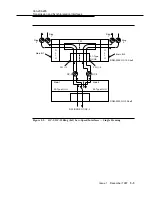

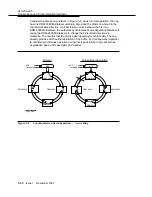

Each DDM-2000 OC-12 Multiplexer can be provisioned to one of three timing modes:

■

Free-running from an internal oscillator

■

Line timing from an incoming optical interface. This timing reference is used to

generate all outgoing signals. Line timing is an intermediate node that derives

timing from the incoming fiber. Loop timing is a special case of line-timing and

is the terminating node that derives timing from the incoming fiber.

■

External timing from the digital synchronization network via DS1 references

(DS1 External).

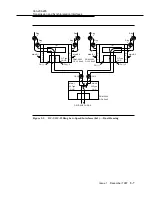

The terms loop timing and line-timing have been changed to clarify timing

terminology. When the OLIU derives local shelf timing from the incoming

optical signal and the shelf is an intermediate shelf (choice of OC-N lines for

timing) in a linear network for example, it is called line-timing. Loop timing is a

subset of line-timing used to describe the timing mode of the terminating node

(single source of timing) of a linear network, for example.

NOTE:

The synchronization and timing examples used throughout this chapter

reference the timing generators as “TG.” This could represent either the BBF2B

TGS or the stratum 3 BBF4 TG3.

Free-Running

5

For free-running operation, the TG derives timing from a temperature-compensated,

voltage-controlled crystal oscillator (TCVCXO) and a digital phase-locked loop

(DPLL) with a full temperature range end-of-life accuracy of

±

15 parts-per-million

(ppm) for the BBF2B TGS, and

±

4.6 ppm for the BBF4 TG3.

Line Timing

5

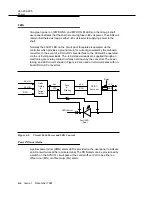

The reference signal feeding the phase-locked loop (PLL) is selected from the

internal oscillator or a line-timing clock derived from the incoming optical line. In line-

timing mode, the OC-12 line being selected for transmission is also selected as the

timing reference.

DS1 External

5

Each TG circuit pack receives one DS1 reference signal which it monitors and from

which it recovers a clock signal. The recovered clock is cross-fed to its companion TG

circuit pack in the same shelf. If the microprocessor on one TG circuit pack detects an

incoming DS1 reference failure, it will signal the microprocessor on the companion

TG circuit pack.