Page 24

Reference Manual

Macro-Tech

®

24x6 & 36x12 Power Amplifiers

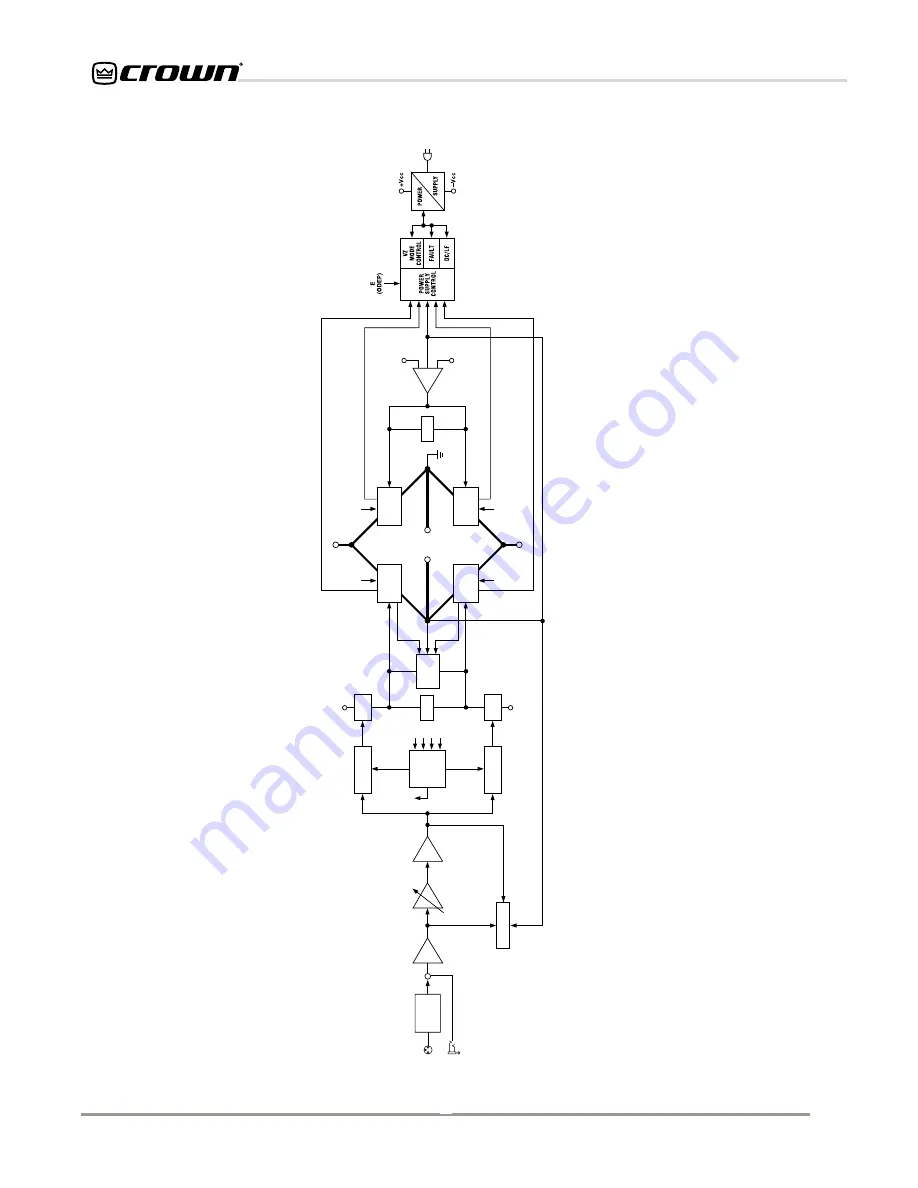

Fig. 5.5 Circuit Block Diagram

(Channel 1)

ONL

Y ONE CHANNEL SHOWN

NPN HI

OUTPUT

STAGE

NPN L

O

W

OUTPUT

STAGE

PNP L

O

W

OUTPUT

STAGE

PNP HI

OUTPUT

STAGE

+

OUTPUT

+Vcc

–

Vcc

TRANSLATOR

LV

A

LV

A

+Vcc

–

Vcc

BIAS

CURRENT

LIMIT

TRANSLATOR

BALANCE

INPUT STAGE

P.I.P.

BALANCED

INPUTS

XLR

VARIABLE

GAIN STAGE

ERROR

AMP

BIAS

BRIDGE

BALANCE

+Vcc

–

Vcc

ODEP

A

B

B

(ODEP)

D

(ODEP)

E

A

(ODEP)

C

(ODEP)

C

D

DISPLAY

1/4" PHONE