H27U1G8F2BTR-BC (DIGITAL : U2603)

H27U1G8F2BTR-BC Pin Function

Rev 1.1 / Sep. 2009

5

1

H27U1G8F2B Series

1 Gbit (128 M x 8 bit) NAND Flash

VCC

VSS

WP

CLE

ALE

RE

WE

CE

IO0~IO7

R/B

NC

NC

NC

NC

NC

NC

NC

NC

CLE

ALE

Vss

Vss

Vss

Vcc

Vcc

NC

NC

NC

WP

RE

CE

WE

RB

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

I/O0

I/O1

I/O9

I/O2

I/O3

I/O10

I/O11

I/O4

I/O15

I/O12

I/O14

I/O13

I/O6

I/O7

I/O5

NC

NC

NC

NC

NC

PRE

I/O8

NC

NC

NC

NC

NC

A

B

C

D

E

F

G

H

J

K

L

M

1 2 3 4 5 6 7 8 9 10

uhukGm

GGGGminh

GGGGGO_P

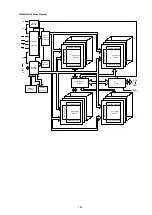

Figure 2 : 48-TSOP1 / 63-FBGA Contact, x8 Device

IO7 - IO0

Data Input / Outputs

CLE

Command latch enable

ALE

Address latch enable

CE

Chip Enable

RE

Read Enable

WE

Write Enable

WP

Write Protect

R/B

Ready / Busy

Vcc

Power Supply

Vss

Ground

NC

No Connection

Figure 1 : Logic Diagram

Table 1 : Signal Names

1&

1&

1&

1&

1&

1&

5%

5(

&(

1&

1&

9FF

9VV

1&

1&

&/(

$/(

:(

:3

1&

1&

1&

1&

1&

1&

1&

1&

1&

,2

,2

,2

,2

1&

1&

1&

9FF

9VV

1&

1&

1&

,2

,2

,2

,2

1&

1&

1&

1&

1$1')ODVK

7623

[

Rev 1.1 / Sep. 2009

6

1

H27U1G8F2B Series

1 Gbit (128 M x 8 bit) NAND Flash

1.2 PIN DESCRIPTION

Table 2 : Pin Description

NOTE :

1. A 0.1uF capacitor should be connected between the Vcc Supply Voltage pin and the Vss Ground pin to decouple the

current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during

program and erase operations.

Pin Name

Description

IO0 ~ IO7

DATA INPUTS/OUTPUTS

The IO pins allow to input command, address and data and to output data during read / program

operations. The inputs are latched on the rising edge of Write Enable (WE). The I/O buffer float to

High-Z when the device is deselected or the outputs are disabled.

CLE

COMMAND LATCH ENABLE

This input activates the latching of the IO inputs inside the Command Register on the Rising edge of

Write Enable (WE).

ALE

ADDRESS LATCH ENABLE

This input activates the latching of the IO inputs inside the Address Register on the Rising edge of

Write Enable (WE).

CE

CHIP ENABLE

This input controls the selection of the device.

WE

WRITE ENABLE

This input acts as clock to latch Command, Address and Data. The IO inputs are latched on the rise

edge of WE.

RE

READ ENABLE

The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is

valid tREA after the falling edge of RE which also increments the internal column address counter by

one.

WP

WRITE PROTECT

The WP pin, when Low, provides an Hardware protection against undesired modify (program / erase)

operations.

R/B

READY BUSY

The Ready/Busy output is an Open Drain pin that signals the state of the memory.

Vcc

SUPPLY VOLTAGE

The Vcc supplies the power for all the operations (Read, Write, Erase).

Vss

GROUND

NC

NO CONNECTION

159