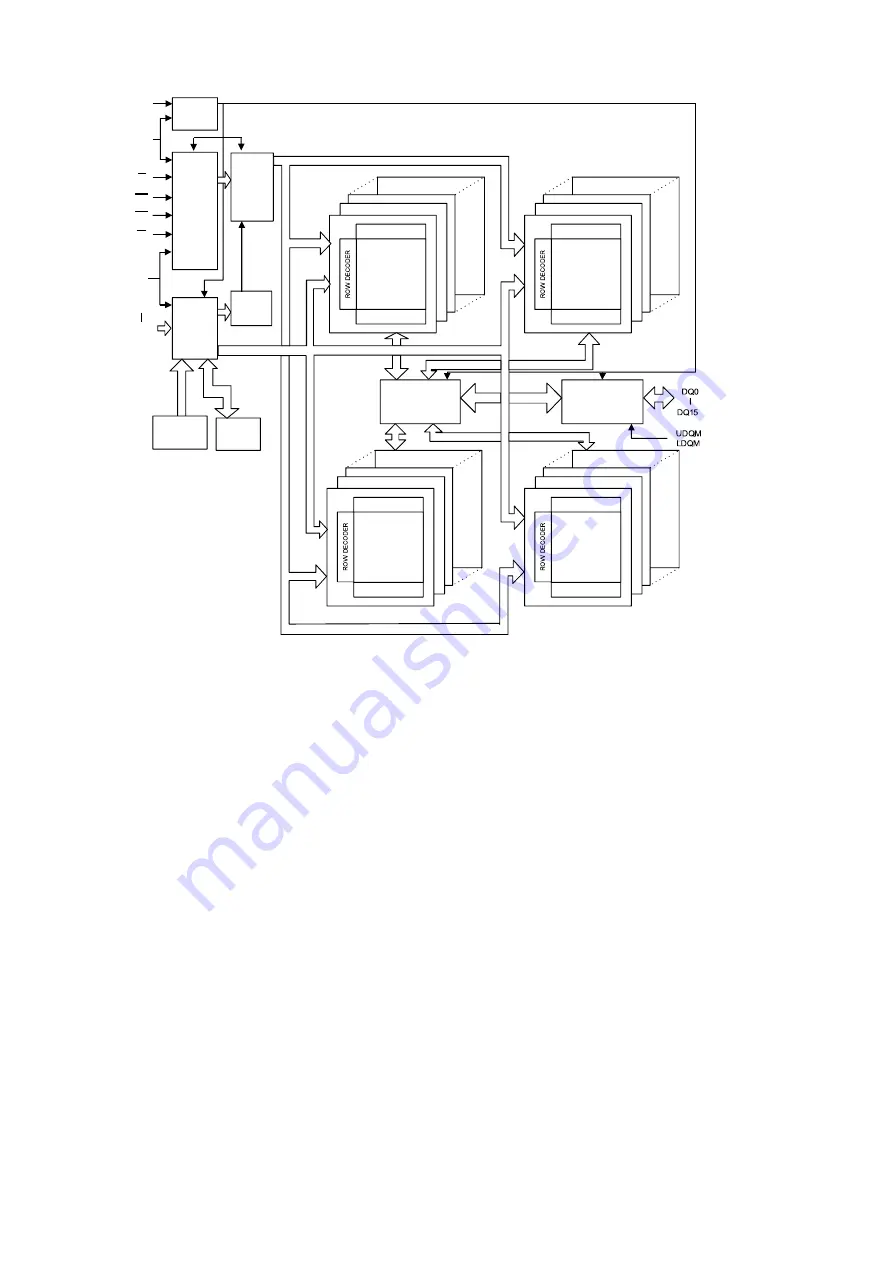

W9864G6KH-5 Block diagram

W9864G6KH

Publication Release Date: Nov. 12, 2013

- 6 -

Revision A02

6. BLOCK DIAGRAM

CLK

CKE

A10

CLOCK

BUFFER

COMMAND

DECODER

ADDRESS

BUFFER

REFRESH

COUNTER

COLUMN

COUNTER

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #2

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #0

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #3

DATA CONTROL

CIRCUIT

DQ

BUFFER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #1

NOTE:

The cell array configuration is 4096 * 256 * 16

A0

A9

BS0

BS1

CS

RAS

CAS

WE

A11

150