Copyright © 2009 Marvell

Doc. No. MV-S105540-00, Rev. --

March 4, 2009, Advance

Document Classification: Proprietary Information

Page 43

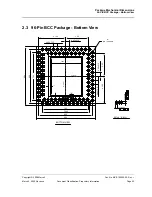

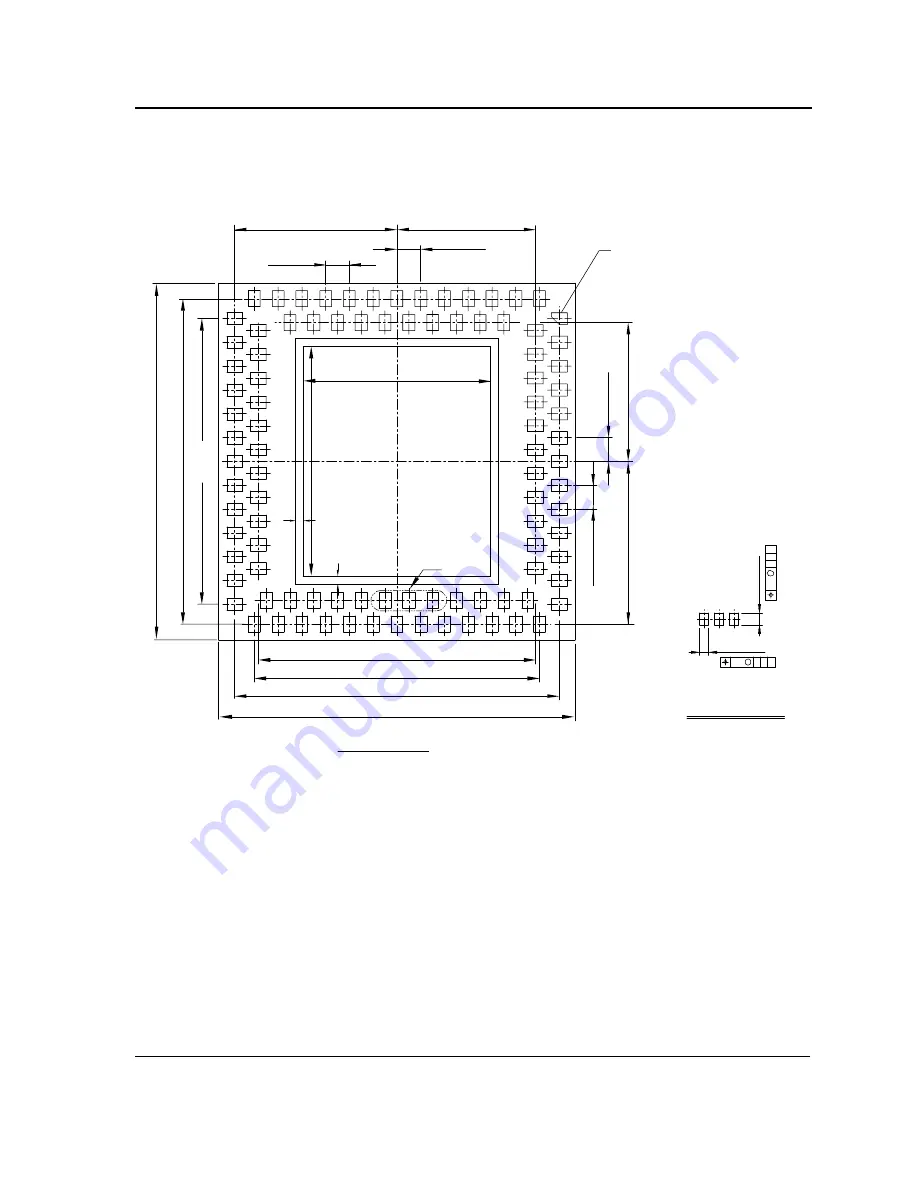

Package Mechanical Dimensions

96-Pin BCC Package - Bottom View

2.3 96-Pin BCC Package - Bottom View

0.

40

±0.05

C

L.

(PKG

.)

''A''

(PIN 1 CORNER)

BOTTOM VIEW

7.200

7.00

8.20

9.00

0.2

0.

2

"B"

4.

10

0

0.

60

0 T

Y

P

.

9.

00

8.

20

4.800

7.

20

5.

80

0

CL.(PKG.)

4.100

0.600 TYP.

3.50

0.60±0.10

0.

60

±0

.1

0

3.

50

DETAIL "B" (95X)

0.30±0.05

Y

X

Z

0.08

Y

X

Z

0.

08

M

M