36

GX5280 User Guide

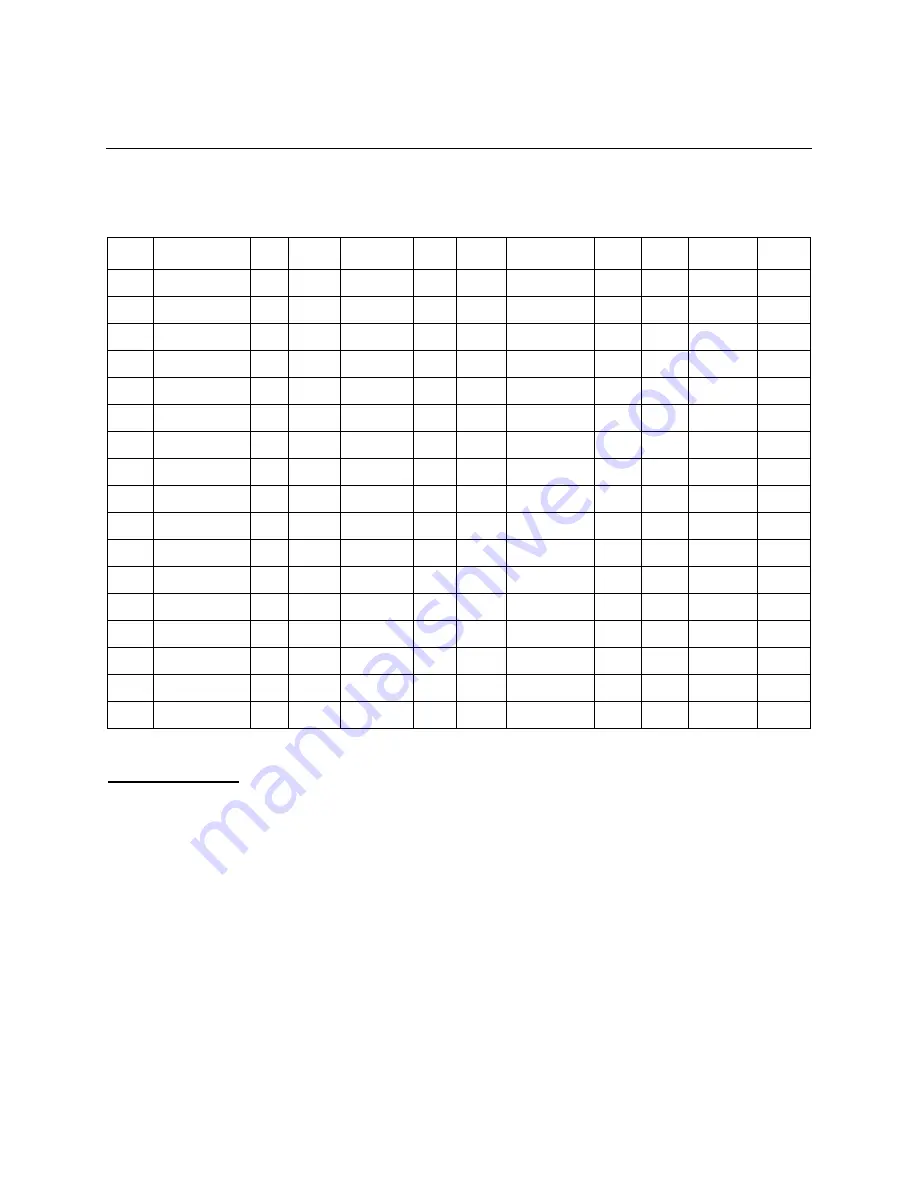

J4 Control Connector

This topic describes the GX5280’s Control connector J4 handles UUT control signals. This interface uses a 68-pin

VHD connector.

The following table defines the DIO to UUT control interface.

Pin

Signal

Type Pin

Signal

Type Pin

Signal

Type

Pin

Signal

Type

1

GND

P

18

GND

P

35

GND

P

52

GND

P

2

N/C

X

19

OEN0n

O

36

N/C

X

53

GND

P

3

GND

X

20

OEN1n

O

37

GND

X

54

GND

P

4

C

X

21

OEN2n

O

38

CLK_LVDS-

X

55

GND

P

5

GND

X

22

OEN3n

O

39

GND

X

56

GND

P

6

GND

P

23

CLK2O

P

40

GND

P

57

GND

P

7

N/C

X

24

XEN0n

I

41

N/C

X

58

GND

P

8

N/C

X

25

XEN1n

I

42

N/C

X

59

GND

P

9

N/C

X

26

XEN2n

I

43

N/C

X

60

GND

P

10

N/C

X

27

XEN3n

I

44

N/C

X

61

GND

P

11

GND

P

28

GND

P

45

GND

P

62

GND

P

12

N/C

X

29

N/C

I

46

N/C

X

63

GND

P

13

N/C

X

30

N/C

X

47

N/C

X

64

GND

P

14

N/C

X

31

5V

P

48

GND

P

65

GND

P

15

N/C

X

32

5V

P

49

GND

P

66

GND

P

16

EXCLK2

X

33

VTH

P

50

GND

P

67

VTH

P

17

EXCLK2O

X

34

GND

P

51

GND

P

68

GND

P

Table A-4: 68-Pin Control Connector Signals, J4.

Notes for Table A-4:

I: Input

O: Output

P: Power/GND

N/C:

Reserved, do not use.

OEN0-3n– Output Enable outputs. A low signal indicates output signal/signals in the indicated byte group is

currently enabled (active low).

XOE0-3n– External Output Enable inputs. A low signal disables the output drivers of the selected I/O group

(active low).

VTH – Termination voltage for data and control signals.

C, CLK_LVDS-:

LVDS clock positive and negative signals (PCB revision D or later, otherwise

N/C).

CLK2O – Output clock distributing external clocks or strobes to slaves (PCB revision D or later, otherwise

N/C).

EXCLK2 – External Clock input #2 (PCB revision D or later, otherwise N/C).

EXCLK2O – Output clock, distributes EXCLK2 to slaves (PCB revision D or later, otherwise N/C).

Summary of Contents for GX5280

Page 2: ......

Page 8: ...vi GX5280 User Guide ...

Page 16: ...8 GX5280 User Guide ...

Page 26: ...18 GX5280 User Guide ...

Page 38: ...30 GX5280 User Guide ...

Page 46: ...38 GX5280 User Guide ...