Processing FPGA 47

Processing FPGA

To reduce the number of image processing tasks that the Host CPU must perform,

the Pro Quad CXP-12 has a Processing FPGA. The Processing FPGA on Matrox

Rapixo CXP Pro is a highly customizable Xilinx Kintex UltraScale KU035

*

. The

Processing FPGA can be configured to offload and even accelerate the most

compute-intensive part of typical image processing applications, without

generating additional data traffic within the host computer (Host).

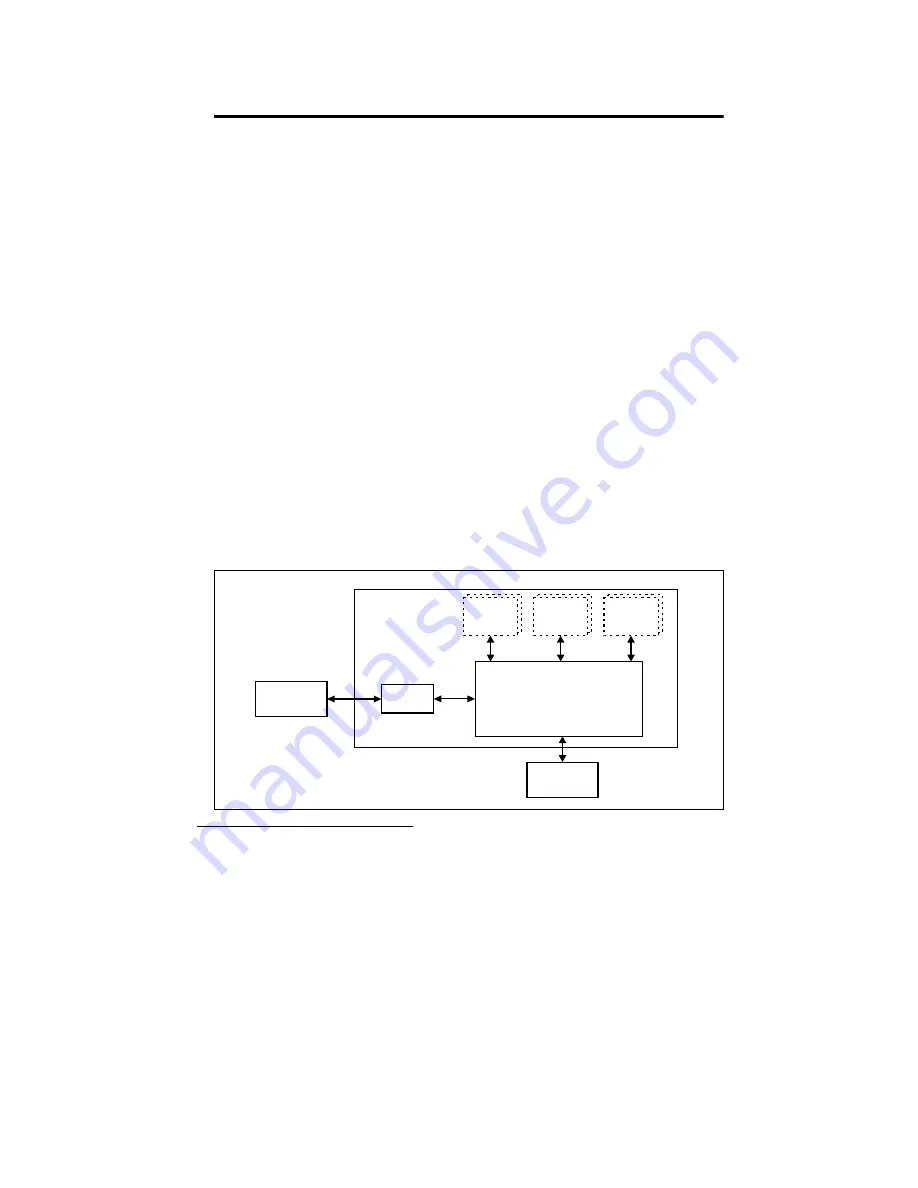

Before the Processing FPGA can process grabbed images, they must be stored in

on-board memory. If images stored in Host memory are required, they can be

streamed directly to the Processing FPGA for processing. Images and other data

resulting from processing can be stored in on-board memory or streamed to the

Host.

The maximum peak bandwidth for images streamed directly to/from Host

memory is 8 Gbyte/sec, as well as for images streamed to/from on-board memory.

Possible processing operations

To use the Processing FPGA, you must configure it with an FPGA configuration

that defines the appropriate functionality. An FPGA configuration is a code

segment that is used to program an FPGA.The following diagram shows the

configurable FPGA components in an FPGA configuration.

*. Other functionality is also implemented through the FPGA, besides customizable

processing, such as the timers and quadrature decoders.

On-board

DDR4

SDRAM

Memory

Controller

AXI

Interconnect

Processing

units

DMA read

to stream

Stream to

DMA write

Host

Interface

Configurable components of an FPGA configuration

Summary of Contents for Matrox Rapixo CXP

Page 6: ......

Page 18: ...18 Chapter 1 Introduction ...

Page 30: ...30 Chapter 2 Hardware installation ...

Page 54: ...54 Appendix A Glossary ...

Page 68: ...68 Appendix B Technical information ...

Page 75: ...Limited warranty Refer to the warranty statement that came with your product ...

Page 76: ......