DS508UM1

45

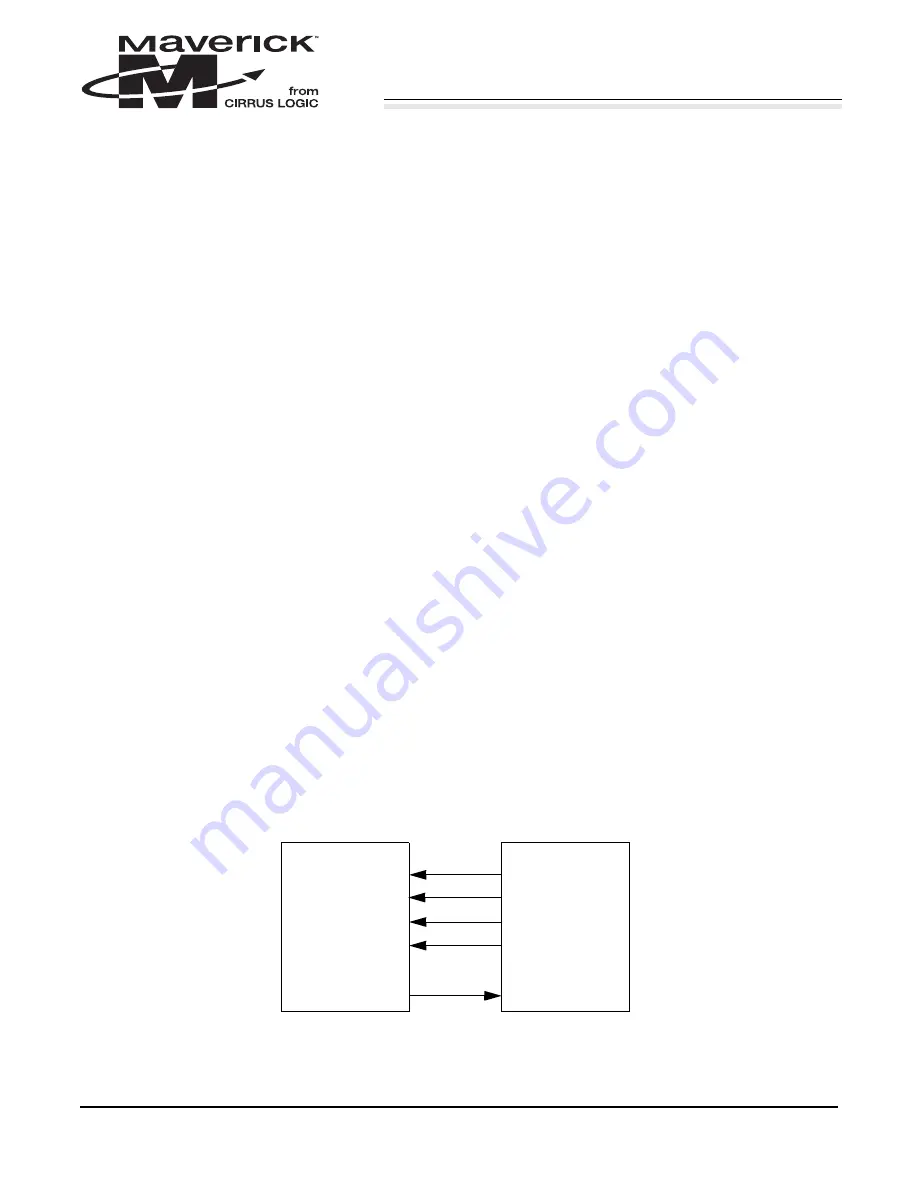

There are five pins to support this SSI port: SSIRXDA, SSITXFR, SSICLK, SSITXDA, and SSIRXFR.

The SSICLK, SSIRXDA, SSIRXFR, and SSITXFR signals are inputs and the SSITXDA signal is an out-

put in slave mode. In the master mode, SSICLK, SSITXDA, SSITXFR, and SSIRXFR are outputs, and

SSIRXDA is an input. Master mode is enabled by writing a one to the SS2MAEN bit (SYSCON2[9]).

When the master / slave SSI is not required, it can be disabled to save power by writing a zero to the

SS2TXEN and the SS2RXEN bits (SYSCON2[4] [7]). When set, these two bits independently enable the

transmit and receive sides of the interface.

The master / slave SSI is synchronous, full duplex, and capable of supporting serial data transfers between

two nodes. Although the interface is byte-oriented, data is loaded in blocks of two bytes at a time. Each

data byte to be transferred is marked by a frame sync pulse, lasting one clock period, and located one clock

prior to the first bit being transferred. Direction of the SSI2 ports, in slave and master mode, is shown in

Figure 9.

Data on the link is sent MSB first and coincides with an appropriate frame sync pulse, of one clock in du-

ration, located one clock prior to the first data bit sent (i.e., MSB). It is not possible to send data LSB first.

When operating in master mode, the clock frequency is selected to be the same as the ADC interface’s

(master mode only SSI1) — that is, the frequencies are selected by the same bits 16 and 17 of the

SYSCON1 register (i.e., the ADCKSEL bits). Thus, the maximum frequency in master mode is

128 kbits/s. The interface will support continuous transmission at this rate assuming that the OS can re-

spond to the interrupts within 1 msec to prevent over/underruns. The timing diagram for this interface can

be found in the AC Characteristics section of this document.

Note:

To allow synchronization to the incoming slave clock, the interface enable bits will not take effect until one

SSICLK cycle after they are written and the value read back from SYSCON2. The enable bits reflect the real

status of the enables internally. Hence, there will be a delay before the new value programmed to the enable

bits can be read back.

Figure 9. SSI2 Port Directions in Slave and Master Mode

Slave EP7312

SSIRXFR

SSITXFR

SSICLK

SSIRXDA

SSITXDA

Master EP7312

SSIRXFR

SSITXFR

SSICLK

SSITXDA

SSIRXDA

Summary of Contents for EP7312

Page 8: ...DS508UM1 9 Part I EP7312 User s Manual...

Page 58: ...DS508UM1 59 Part II Pin and Register Reference...

Page 122: ......