80

DS508UM1

6.2.4

SYSFLG1 — System Status Flags Register

ADDRESS: 0x8000.0140

The system status flags register is a 32-bit read only register, which indicates various system infor-

mation. The bits in the system status flags register SYSFLG1 are defined in Table 38.

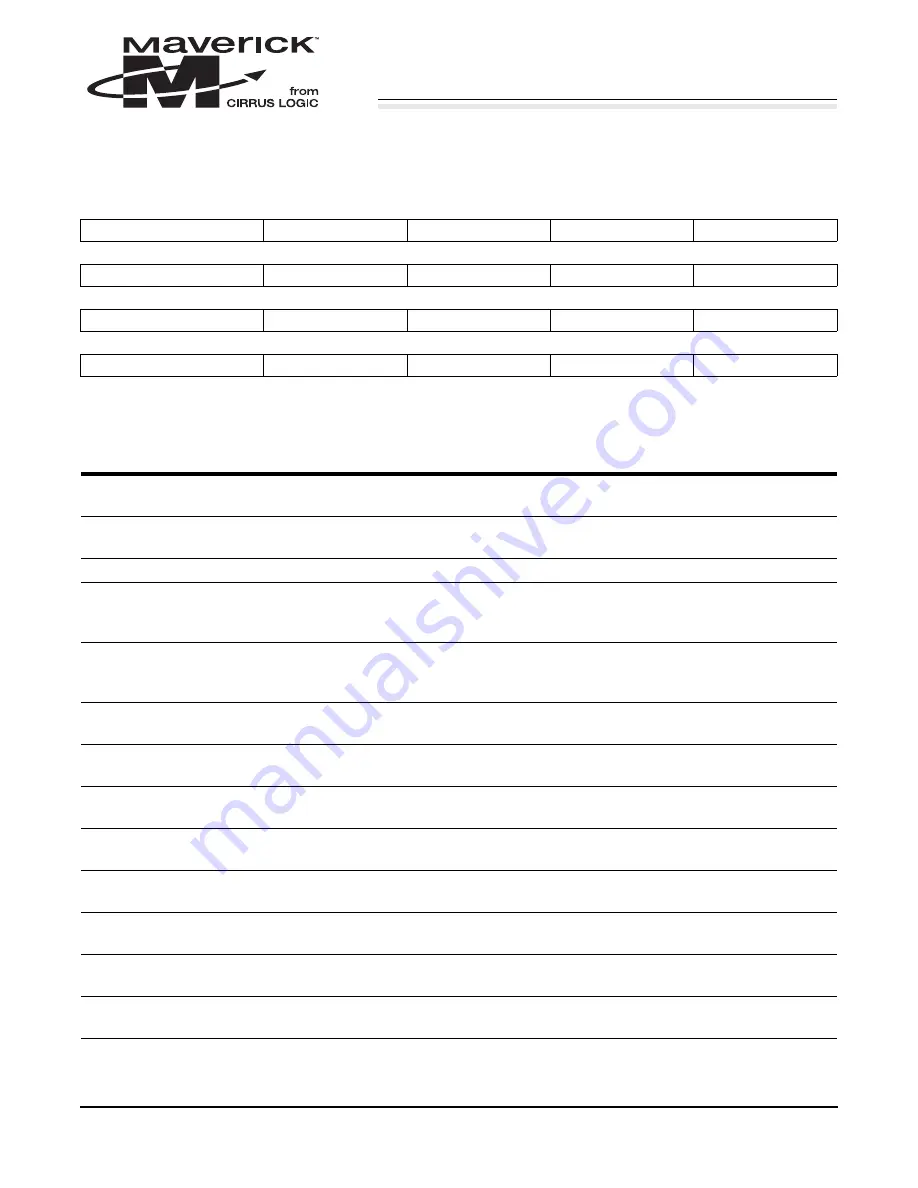

31-30

29

28

27

26

VERID

ID

BOOTBIT1

BOOTBIT0

SSIBUSY

23

22

21-16

23

22

UTXFF1

URXFE1

RTCDIV

UTXFF1

URXFE1

15

14

13

12

11

CLDFLG

PFFLG

RSTFLG

NBFLG

UBUSY1

7-4

3

2

1

0

DID

WUON

WUDR

DCDET

MCDR

Bit

Description

0

MCDR: Media changed direct read. This bit reflects the INVERTED non-latched status of the

media changed input.

1

DCDET: This bit will be set if a non-battery operated power supply is powering the system (it is

the inverted state of the nEXTPWR input pin).

2

WUDR: Wake up direct read. This bit reflects the non-latched state of the wakeup signal.

3

WUON: This bit will be set if the system has been brought out of the Standby State by a rising

edge on the wakeup signal. It is cleared by a system reset or by writing to the HALT or STDBY

locations.

4-7

DID: Display ID nibble. This 4-bit nibble reflects the latched state of the four LCD data lines. The

state of the four LCD data lines is latched by the LCDEN bit, and so it will always reflect the last

state of these lines before the LCD controller was enabled.

8

CTS: This bit reflects the current status of the clear to send (CTS) modem control input to

UART1.

9

DSR: This bit reflects the current status of the data set ready (DSR) modem control input to

UART1.

10

DCD: This bit reflects the current status of the data carrier detect (DCD) modem control input to

UART1.

11

UBUSY1: UART1 transmitter busy. This bit is set while UART1 is busy transmitting data, it is

guaranteed to remain set until the complete byte has been sent, including all stop bits.

12

NBFLG: New battery flag. This bit will be set if a low to high transition has occurred on the

nBATCHG input, it is cleared by writing to the STFCLR location.

13

RSTFLG: Reset flag. This bit will be set if the RESET button has been pressed, forcing the

nURESET input low. It is cleared by writing to the STFCLR location.

14

PFFLG: Power Fail Flag. This bit will be set if the system has been reset by the nPWRFL input

pin, it is cleared by writing to the STFCLR location.

15

CLDFLG: Cold start flag. This bit will be set if the EP7312 has been reset with a power on reset,

it is cleared by writing to the STFCLR location.

Table 38. SYSFLG1

Summary of Contents for EP7312

Page 8: ...DS508UM1 9 Part I EP7312 User s Manual...

Page 58: ...DS508UM1 59 Part II Pin and Register Reference...

Page 122: ......