32

DS508UM1

2.11

CL-PS6700 PC Card Controller Interface

Two of the expansion memory areas are dedicated to supporting up to two CL-PS6700 PC Card controller

devices. These are selected by nCS[4] and nCS[5] (must first be enabled by bits 5 and 6 of SYSCON2).

For efficient, low power operation, both address and data are carried on the lower 16 bits of the EP7312

data bus.

Accesses are initiated by a write or read from the area of memory allocated for nCS[4] or nCS[5]. The

memory map within each of these areas is segmented to allow different types of PC Card accesses to take

place, for attribute, I/O, and common memory space. The CL-PS6700 internal registers are memory

mapped within the address space as shown in Table 15.

Note:

Due to the operating speed of the CL-PS6700, this interface is supported only for processor speeds of

13 and 18 MHz.

A complete description of the protocol and AC timing characteristics can be found in the CL-PS6700 data

sheet. A transaction is initiated by an access to the nCS[4] or nCS[5] area. The chip select is asserted, and

on the first clock, the upper 10 bits of the PC Card address, along with 6 bits of size, space, and slot infor-

mation are put out onto the lower 16 bits of the EP7312’s data bus. Only word (i.e., 4-byte) and single-byte

accesses are supported, and the slot field is hardcoded to 11, since the slot field is defined as a “Reserved

field” by the CL-PS6700. The chip selects are used to select the device to be accessed. The space field is

made directly from the A26 and A27 CPU address bits, according to the decode shown in Table 16 on

page 33. The size field is forced to 11 if a word access is required, or to 00 if a byte access is required. This

avoids the need to configure the interface after a reset. On the second clock cycle, the remaining 16 bits of

the PC Card address are multiplexed out onto the lower 16 bits of the data bus. If the transaction selected

is a CL-PS6700 register transaction, or a write to the PC Card (assuming there is space available in the CL-

PS6700’s internal write buffer) then the access will continue on the following two clock cycles. During

these following two clock cycles the upper and lower halves of the word to be read or written will be put

onto the lower 16 bits of the main data bus.

The “ptype” signal on the CL-PS6700s should be connected to the EP7312’s WRITE output pin. During

PC Card accesses, the polarity of this pin changes, and it becomes low to signify a write and high to signify

a read. It is valid with the first half word of the address. During the second half word of the address, it is

always forced high to indicate to the CL-PS6700 that the EP7312 has initiated either the write or read.

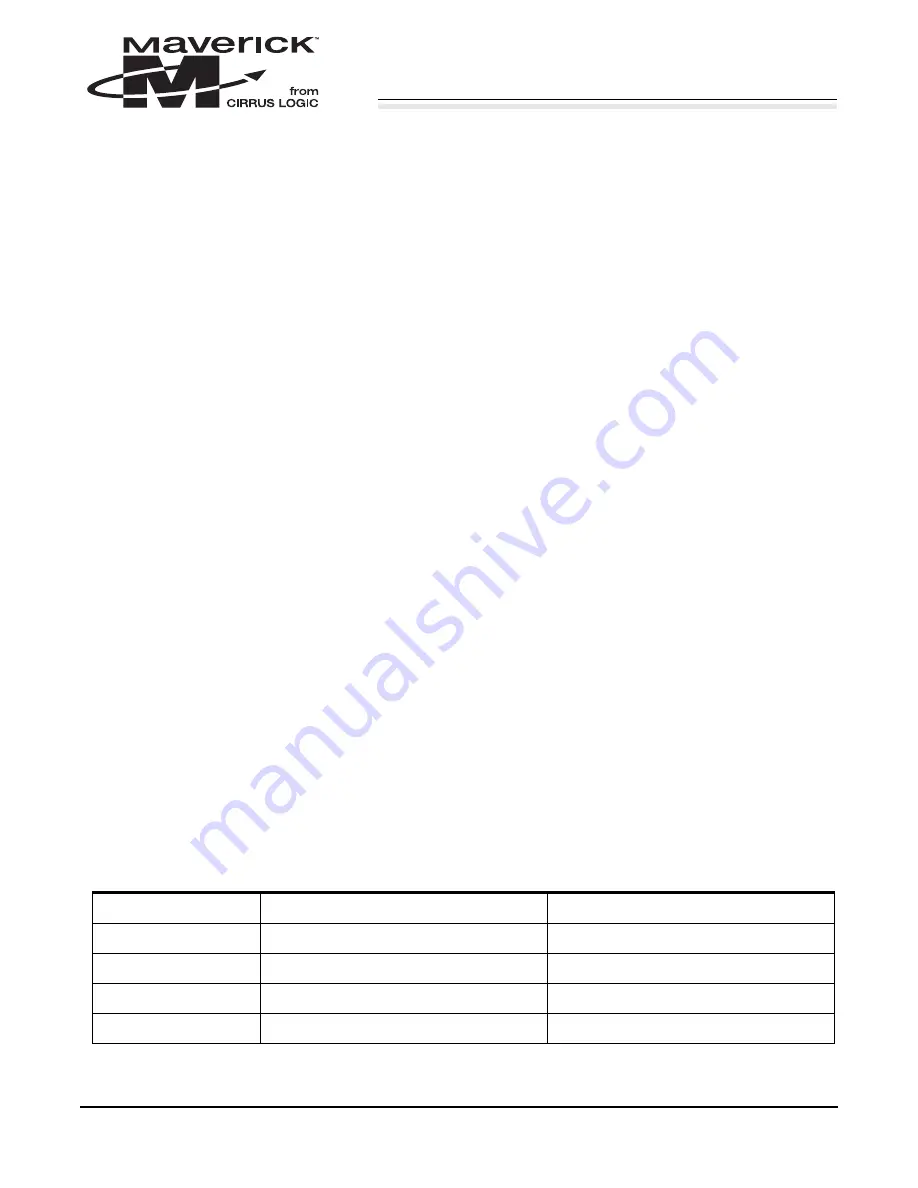

Access Type

Addresses for CL-PS6700 Interface 1

Addresses for CL-PS6700 Interface 2

Attribute

0x4000.0000–0x43FFFFFF

0x5000.0000– 0x53FFFFFF

I/O

0x4400.0000–0x47FFFFFF

0x5400.0000–0x57FFFFFF

Common memory

0x4800.0000–0x4BFFFFFF

0x5800.0000–0x5BFFFFFF

CL-PS6700 registers

0x4C00.0000–0x4FFFFFFF

0x5C00.0000–0x5FFFFFFF

Table 15. CL-PS6700 Memory Map

Summary of Contents for EP7312

Page 8: ...DS508UM1 9 Part I EP7312 User s Manual...

Page 58: ...DS508UM1 59 Part II Pin and Register Reference...

Page 122: ......