MAX32600 User’s Guide

Communication Peripherals

7.1 I²C

7.1.8

Registers (I2CM)

7.1.8.1

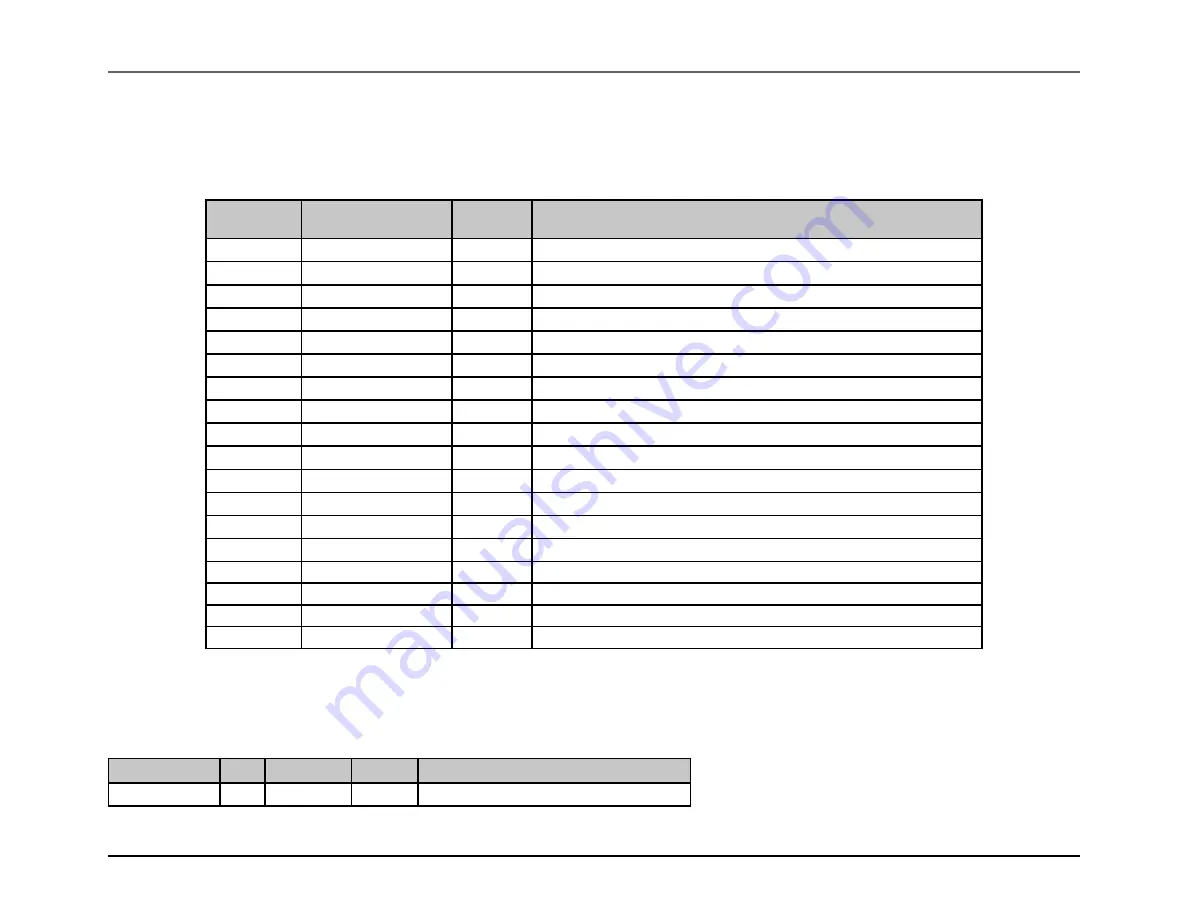

Module I2CM Registers

Address

Register

32b

Word Len

Description

0x40040000

1

Full Speed SCL Clock Settings

0x4004000C

1

[TO_CNTL] Timeout and Auto-Stop Settings

0x40040010

1

[EN_CNTL] I2C Master Control Register

0x40040014

1

[MSTR_CNTL] I2C Master Transaction Start and Status Flags

0x40040018

1

Interrupt Flags

0x4004001C

1

Interrupt Enable/Disable Controls

0x40040028

1

Bit-Bang Control Register

0x40042000

1

Full Speed SCL Clock Settings

0x4004200C

1

Timeout and Auto-Stop Settings

0x40042010

1

I2C Master Control Register

0x40042014

1

I2C Master Transaction Start and Status Flags

0x40042018

1

Interrupt Flags

0x4004201C

1

Interrupt Enable/Disable Controls

0x40042028

1

Bit-Bang Control Register

0x40103000

512

I2C Master 0 Transaction FIFO

0x40103800

512

I2C Master 0 Results FIFO

0x4010D000

512

I2C Master 1 Transaction FIFO

0x4010D800

512

I2C Master 1 Results FIFO

7.1.8.1.1

I2CMn_FS_CLK_DIV

I2CMn_FS_CLK_DIV.fs_filter_clk_div

Field

Bits

Default

Access

Description

fs_filter_clk_div

7:0

00000001b

R/W

Full Speed Filter Clock Divisor

Rev.1.3 April 2015

Maxim Integrated

Page 230