MAX32600 User’s Guide

System Configuration and Management

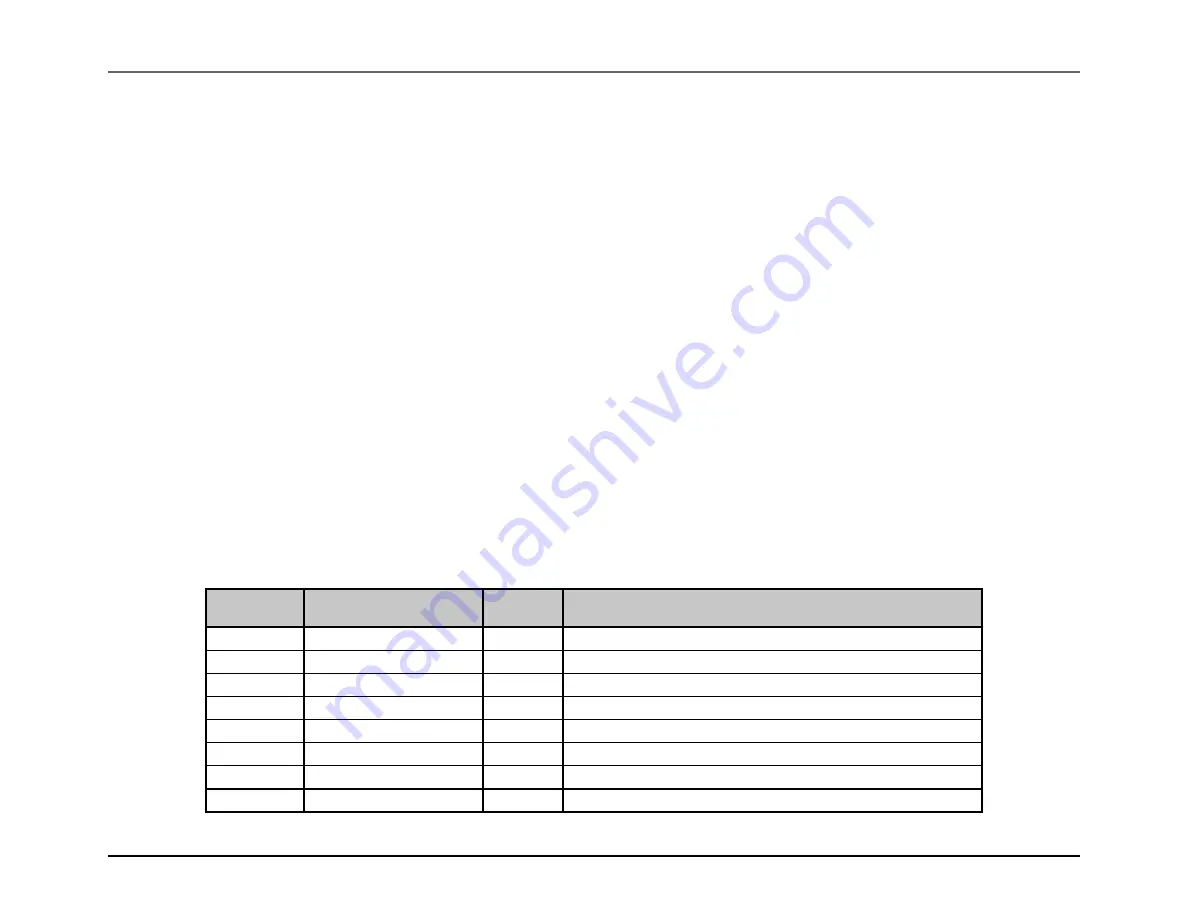

4.4 Registers (IOMAN)

• Reset generated by ARM core due to lockup condition.

• Reset generated by watchdog timer.

4.3.2

Power-On Reset

The Power-On Reset or POR on the

MAX32600

resets all functions and blocks that are reset by a System Reset, but also resets additional blocks and registers

including certain system configuration registers and the ARM JTAG debugging engine on the Cortex-M3 core.

A POR reset is triggered when a power failure occurs on either the digital main supplies (V

DD

and V

BUS

) or the V

REG18

supply that is used to maintain the state of the

digital core.

The POR reset does not affect the state of certain registers and blocks, including the power sequencer, the dynamic tamper sensor, and the RTC.

4.3.3

RTC POR

When a standard POR occurs, the state of the RTC and certain other registers and blocks are still retained as long as the backup supply VRTC is still available.

A failure of the V

RTC

supply in combination with a standard POR causes a full reset of the RTC core and all registers and internal state on the device (apart from

information retained in non-volatile flash storage). This is referred to as an RTC POR.

4.4

Registers (IOMAN)

4.4.1

Module IOMAN Registers

Address

Register

32b

Word Len

Description

0x40090C00

1

Wakeup Detect Mode Request Register 0 (P0/P1/P2/P3)

0x40090C04

1

Wakeup Detect Mode Request Register 1 (P4/P5/P6/P7)

0x40090C08

1

Wakeup Detect Mode Acknowledge Register 0 (P0/P1/P2/P3)

0x40090C0C

1

Wakeup Detect Mode Acknowledge Register 1 (P4/P5/P6/P7)

0x40090C10

1

Analog Input Request Register 0 (P0/P1/P2/P3)

0x40090C14

1

Analog Input Request Register 1 (P4/P5/P6/P7)

0x40090C18

1

Analog Input Acknowledge Register 0 (P0/P1/P2/P3)

0x40090C1C

1

Analog Input Acknowledge Register 1 (P4/P5/P6/P7)

Rev.1.3 April 2015

Maxim Integrated

Page 103