MAX32600 User’s Guide

Communication Peripherals

7.2 SPI

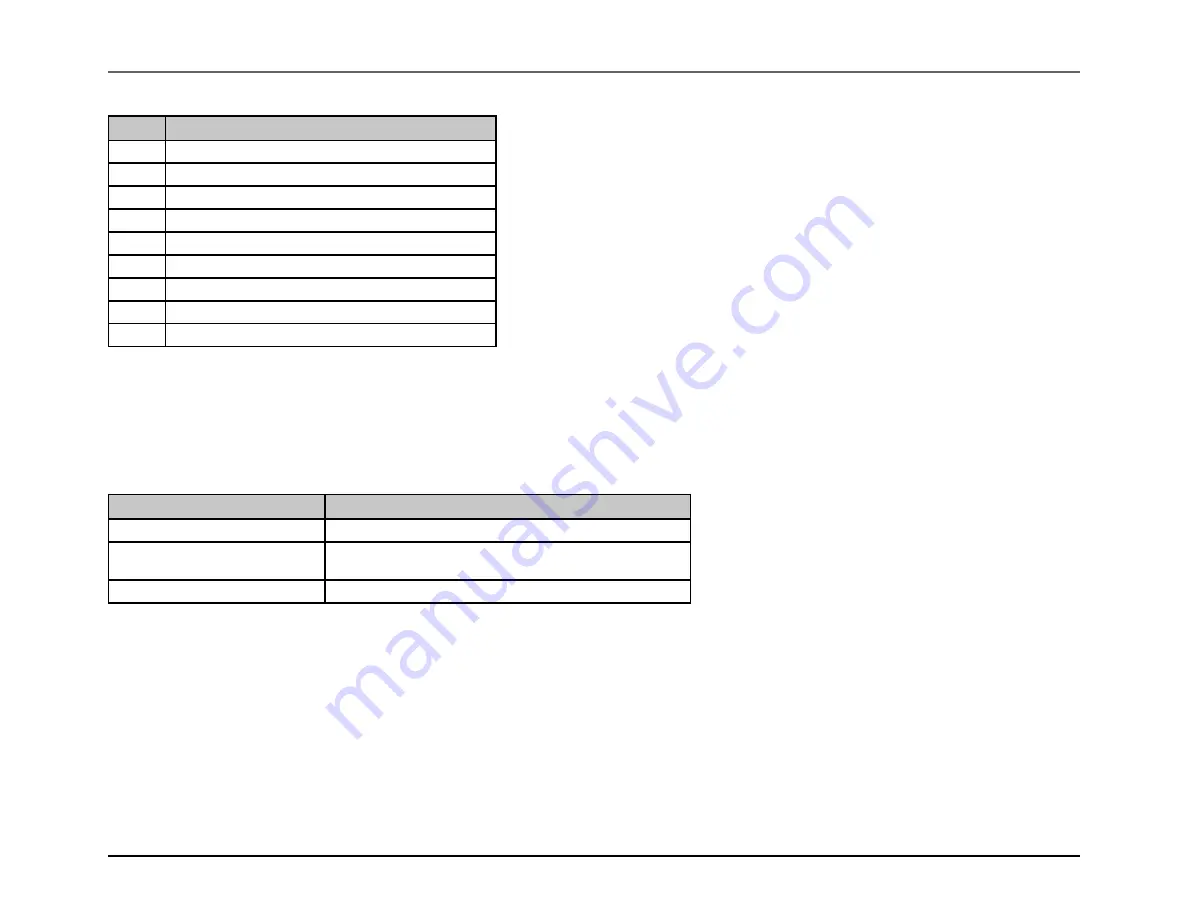

[3:0]

SPI Clock Rate

0010b

(System Clock Source / 2)

0011b

(System Clock Source / 4)

0100b

(System Clock Source / 8)

0101b

(System Clock Source / 16)

0110b

(System Clock Source / 32)

0111b

(System Clock Source / 64)

1000b

(System Clock Source / 128)

1001b

(System Clock Source / 256)

other

(System Clock Source / 1)

7.2.3.1

Clock Gating

Clock gating for the SPI ports is controlled by the register fields

CLKMAN_CLK_GATE_CTRL1.spi0_clk_gater

CLKMAN_CLK_GATE_CTRL1.spi1_clk_gater

, and

CLKMAN_CLK_GATE_CTRL1.spi2_clk_gater

. The table below shows the supported settings for the

spi[x]_clk_gater

register fields and their meanings.

Clock Control -

CLKMAN_CLK_GATE_CTRL1.spi[x]_clk_gater

SPI[x] Clock Control Value (2b)

Setting

00b

Clock off - SPI[x] disabled

01b

Dynamic Clock Gating Enabled - SPI[x] clock active only

when used

10b or 11b

Clock on - SPI[x] enabled at all times

7.2.4

Configuration Modes Overview

Once the main SPI clock is set up for the port, the remainder of the configuration and operation for SPI is mapped into three categories:

•

Static Configuration:

Performed during SPI initial setup and/or when SPI is not active.

–

–

•

Dynamic Configuration:

Configuration required to communicate with a specific slave device, which may take place while the SPI port is active.

Rev.1.3 April 2015

Maxim Integrated

Page 263