MAX32600 User’s Guide

Communication Peripherals

7.2 SPI

0:Int not active, 1:Interrupt has been triggered Set when the results FIFO is in the ’almost full’ state.

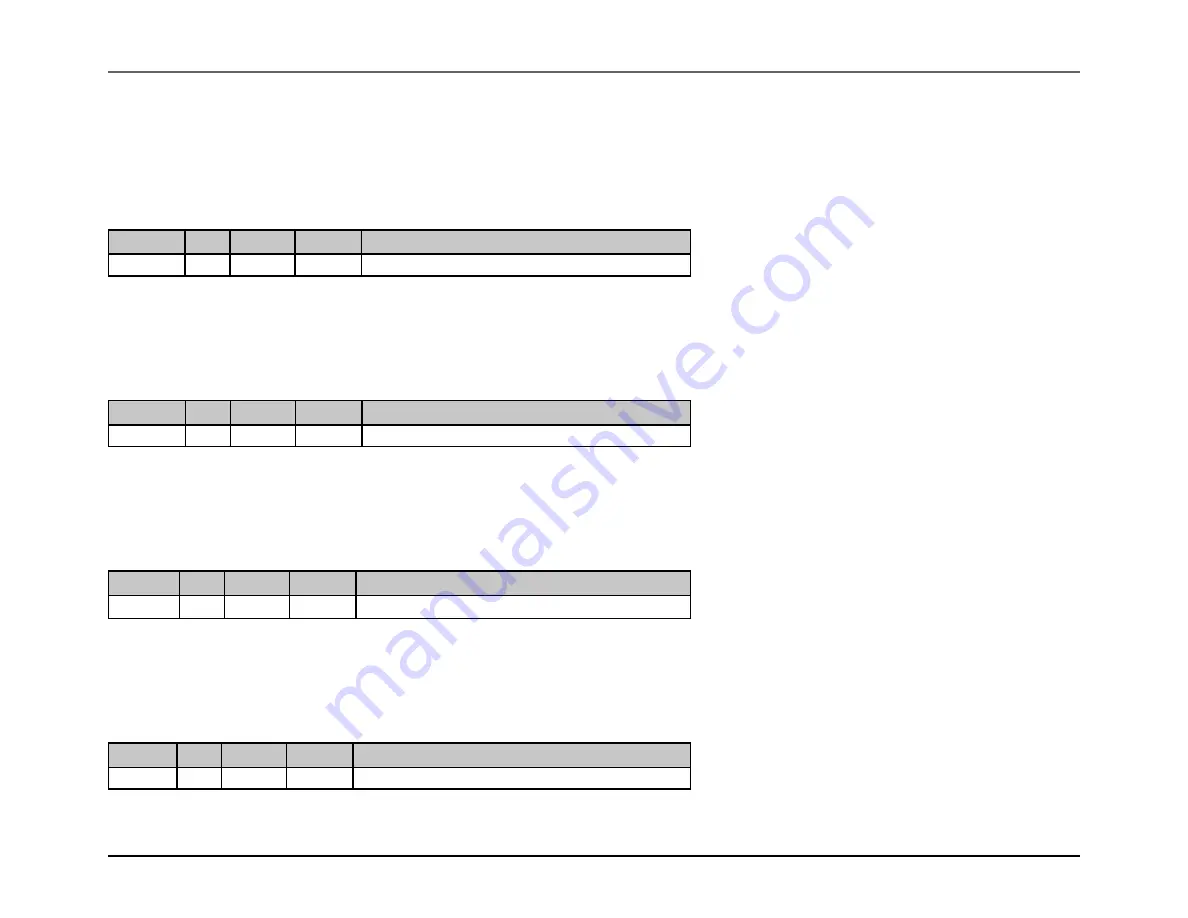

7.2.9.1.7

SPIn_INTEN

SPIn_INTEN.tx_stalled

Field

Bits

Default

Access

Description

tx_stalled

0

0

R/W

Transaction Stalled Int Enable

0: Interrupt source disabled; 1:Interrupt enabled.

SPIn_INTEN.rx_stalled

Field

Bits

Default

Access

Description

rx_stalled

1

0

R/W

Results Stalled Int Enable

0: Interrupt source disabled; 1:Interrupt enabled.

SPIn_INTEN.tx_ready

Field

Bits

Default

Access

Description

tx_ready

2

0

R/W

Transaction Ready Int Enable

0: Interrupt source disabled; 1:Interrupt enabled.

SPIn_INTEN.rx_done

Field

Bits

Default

Access

Description

rx_done

3

0

R/W

Results Done Int Enable

Rev.1.3 April 2015

Maxim Integrated

Page 281