MAX32600 User’s Guide

Analog Front End

8.3 ADC

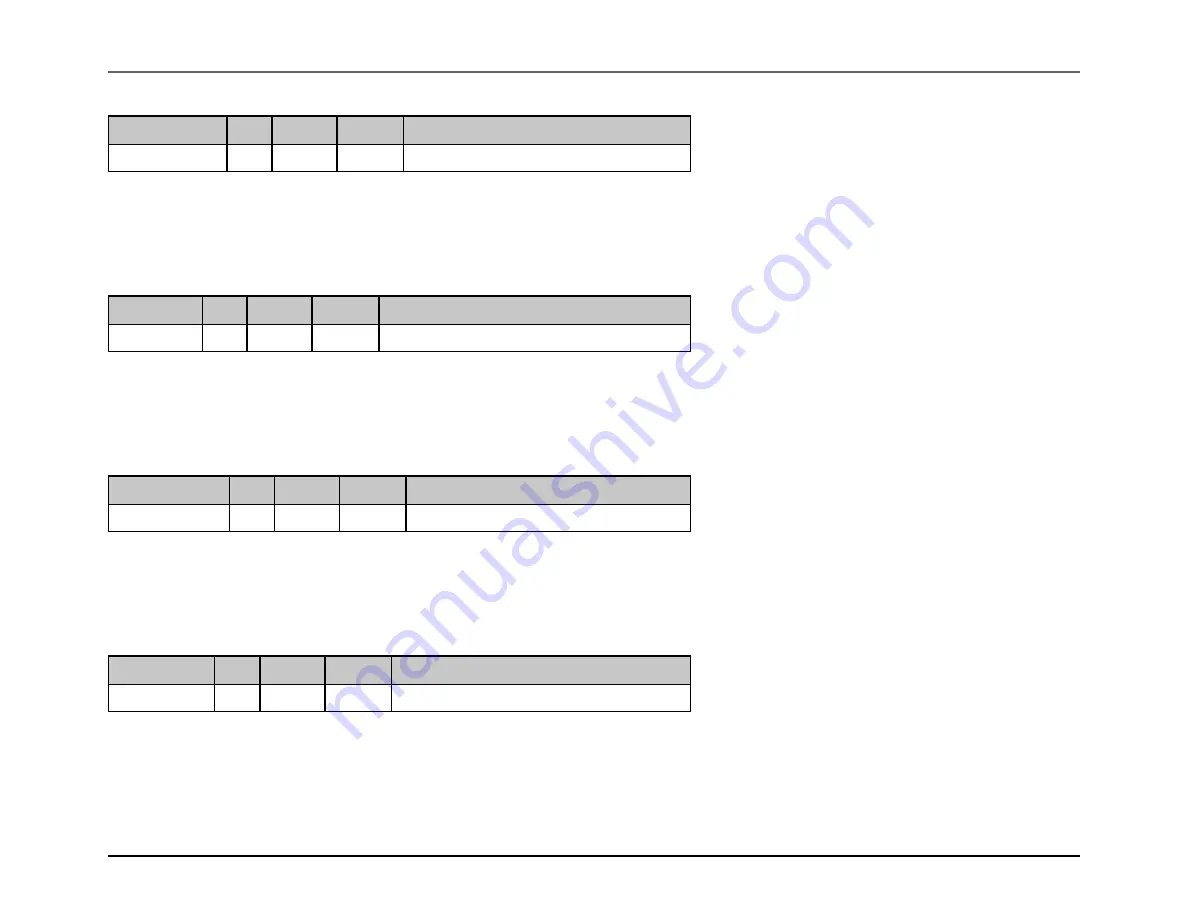

Field

Bits

Default

Access

Description

cpu_pga_trk_dly

4

1

R/W

Reserved Field - Do Not Modify

This field should not be modified by the user. For proper operation, this field must be left at its default value.

ADC_PGA_CTRL.cpu_pga_trk

Field

Bits

Default

Access

Description

cpu_pga_trk

5

0

R/W

Reserved Field - Do Not Modify

This field should not be modified by the user. For proper operation, this field must be left at its default value.

ADC_PGA_CTRL.cpu_pga_bypass

Field

Bits

Default

Access

Description

cpu_pga_bypass

6

0

R/W

PGA Bypass Control

0: Normal mode, PGA path active 1: PGA bypass, input mux drives ADC

ADC_PGA_CTRL.pga_wake_cnt

Field

Bits

Default

Access

Description

pga_wake_cnt

12:8

5’15h

R/W

PGA Wakeup Counter

Length of time (defined in number of ADC clocks) that is allowed for the PGA to turn on. Minimum is 15h. Longer values would allow longer PGA acquisition time on

first sample or during reduced sample rate modes.

Rev.1.3 April 2015

Maxim Integrated

Page 431