PCI-DAS1602/12 User's Guide

Specifications

24

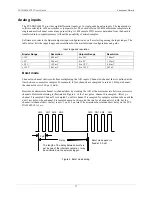

Table 8. Accuracy components (errors in LSBs)

Range

Gain Error (LSB)

Offset Error (LSB)

DLE (LSB)

ILE (LSB)

±10 V

±2.0 max

±0.1 max

±1.0 max

±1.0 max

±5 V

±2.0 max

±0.2 max

±1.0 max

±1.0 max

0 to +10 V

±2.0 max

±0.2 max

±1.0 max

±1.0 max

0 to +5 V

±2.0 max

±0.4 max

±1.0 max

±1.0 max

Each PCI-DAS1602/12 is tested at the factory to assure the board’s overall error does not exceed ±3.0 LSB.

Total board error is a combination of gain, offset, integral linearity and differential linearity error. The

theoretical worst-case error of the board may be calculated by summing these component errors. Worst case

error is realized only in the unlikely event that each of the component errors are at their maximum level, and

causing error in the same direction. Although an examination of the chart and a summation of the maximum

theoretical errors shows that the board could theoretically exhibit a ±4.4 LSB error, our testing assures this

error is never realized in a board that we ship.

Analog output pacing and triggering

Table 9. Analog output pacing and triggering specifications

D/A pacing

(SW programmable)

Internal counter

External source (D/A EXTERNAL PACER)

Software paced

D/A trigger Modes

External digital (EXTERNAL D/A PACER GATE)

Software triggered

Data transfer

From 1024 sample FIFO via REPOUTSW mode. Data interleaved for dual analog output mode.

Programmed I/O

Update DACs individually or simultaneously (SW selectable)

Throughput

250 KHz max per channel, 2 channels simultaneous

Digital input/output

Table 10. Digital input/output specifications

Digital type

82C55

Number of I/O

24 (FIRSTPORTA Bit 0 through FIRSTPORTC Bit 7)

Configuration

2 banks of 8 and 2 banks of 4 or

3 banks of 8 or

2 banks of 8 with handshake

Input high voltage

2.0 V min, 5.5 V absolute max

Input low voltage

0.8 V max, –0.5 V absolute min

Output high voltage

(IOH = -2.5 mA)

3.0 V min

Output low voltage

(IOL = 2.5 mA)

0.4 V max

Power-up / reset state

Input mode (high impedance)

Summary of Contents for PCI-DAS1602

Page 1: ......