Digital input/output

Table 3. Digital input/output specifica ons

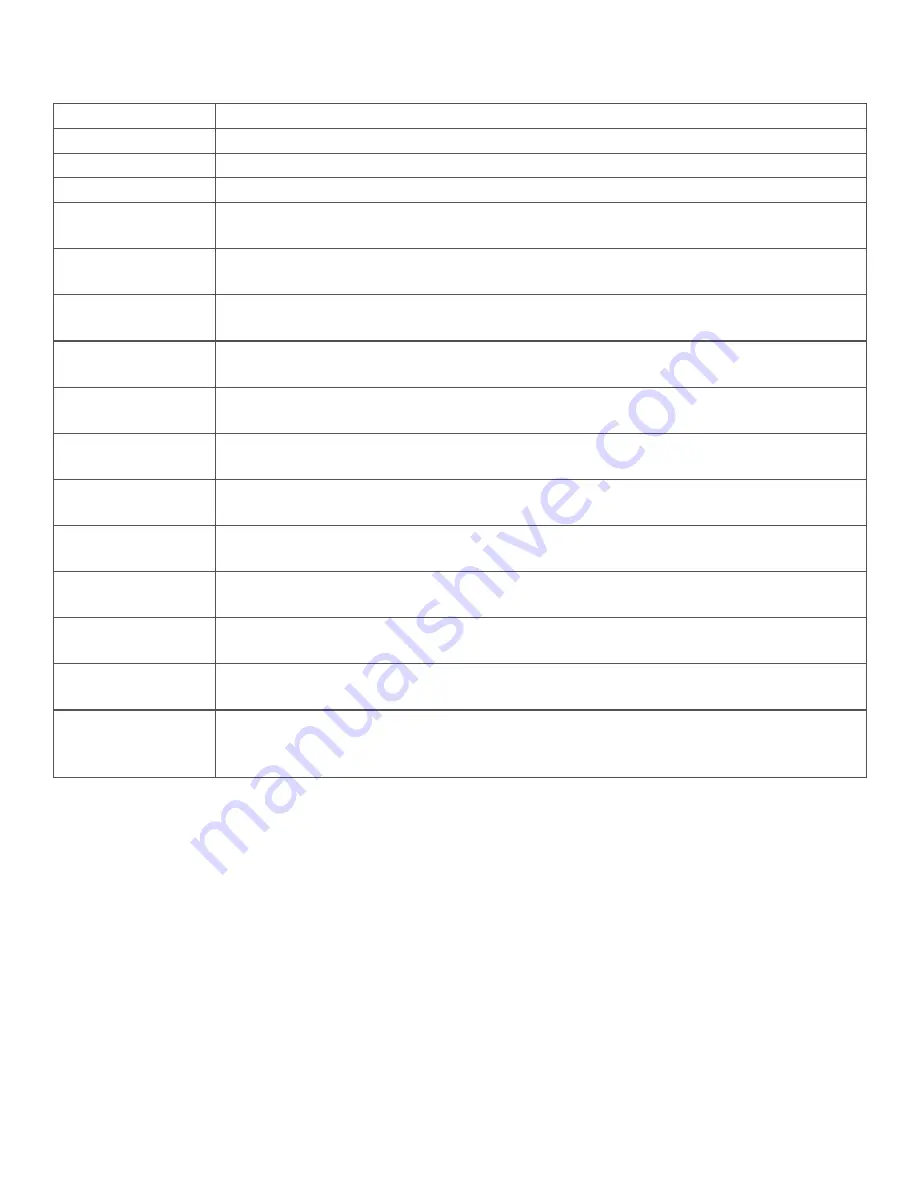

Parameter

Specifica on

Digital type

CMOS (Schmi trigger) input / open drain output

Number of I/O

One port of 4 bits

Configura on

Each bit can be independently configured for input or output

Power on

condi ons

Power on reset is input mode

Pull-up

configura on

Each bit is pulled up to 5 V with a 100 kΩ resistor

Input frequency

range

Input high voltage

threshold

1.9 V min, 3.6 V max

Input low voltage

threshold

2.3 V max, 1.0 V min

Schmi trigger

hysteresis

0.6 V min, 1.7 V max

Input high voltage

limit

15 V max

Input low voltage

limit

–0.5 V absolute min

0 V recommended min

Output voltage

range

0 V to +5 V (no external pull up resistor)

0 V to +15 V max (

Output off state

leakage current

10 µA max

Output sink

current capability

100 mA max (con nuous) per output pin

Output transistor

on-resistance

(drain to source)

1.6 Ω

Note 1. Applying a signal with a frequency higher than this specifica on will adversely affect system

performance and could cause errors.

Note 2. The external pull-up resistor is connected between the digital output bit and an external supply. Adding

an external pull-up resistor connects it in parallel with the internal 100 kΩ pull-up resistor of that par cular

digital input/output bit to the internal 5 V supply. Careful considera on should be made when considering the

external pull-up resistor value and the resultant pull-up voltage produced at the load.

WebDAQ 316 User's Guide

page 23