5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

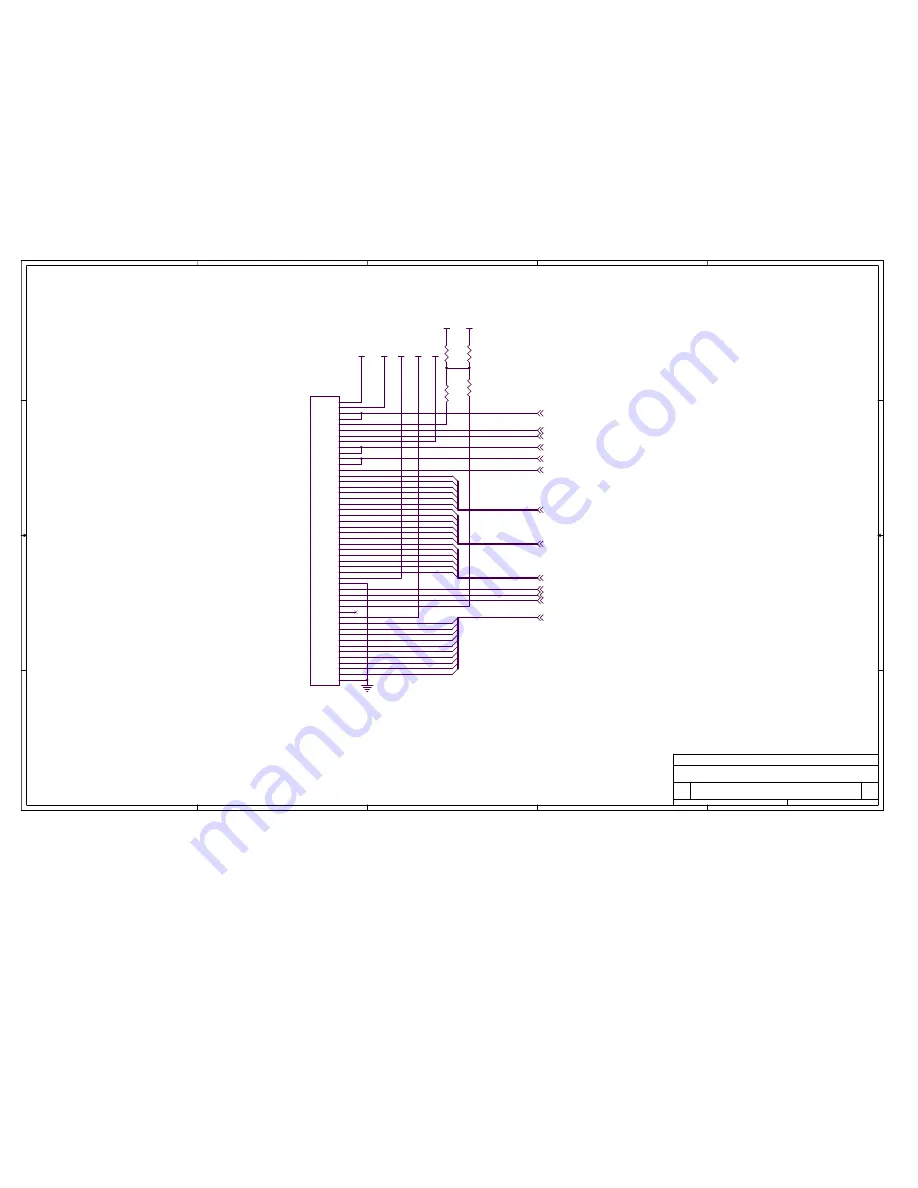

HR TFT FLAT PANEL INTERFACE PAGE 2

SHARP HR TFT INTERFACE

HR-TFT interface #2

<Doc>

2

MQ-1168 Evaluation Design

B

4

11

Tuesday, April 16, 2002

Title

Size

Document Number

Rev

Date:

Sheet

of

FP_G5

FP_G2

FP_B1

FP_R4

V3

FP_R2

FP_G0

FP_R1

FP_G[5..0]

V4

V[9..0]

FP_B3

FP_R5

V8

FP_HSCAN_DIR

FP_G4

FP_VSCAN_DIR

FP_DESPL

FP_B5

VEE_AC_DC

FP_R0

FP_B[5..0]

FP_B4

FP_PWM1

V7

FP_B2

FVSYNC

V6

FP_R3

FP_B0

V5

FP_LP

FP_G3

FP_R[5..0]

V0

VCOM_AC_DC

V2

FLCLK

V1

FP_MODE

FP_G1

FP_SCLK

V9

FP_PWM1

1,5

FVSYNC

1,5

FLCLK

1,5

FP_SCLK

1,5

FP_DESPL

1,5

FP_R[5..0]

1,5

FP_G[5..0]

1,5

FP_B[5..0]

1,5

V[9..0]

3

VEE_AC_DC

3

VCOM_AC_DC 3

FP_LP

1,5

FP_MODE_G5 1,2,5

+15V

3.3V

-11.7V

-15V

5V

3.3V

3.3VBUS

R6

0

U1

FCON50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

R3

10K

R7

0

R2

10K