MeiG

Product

Manual

of

SLM750

Module

SLM750

Module

Hardware

Design

Page 17, total 84 pages

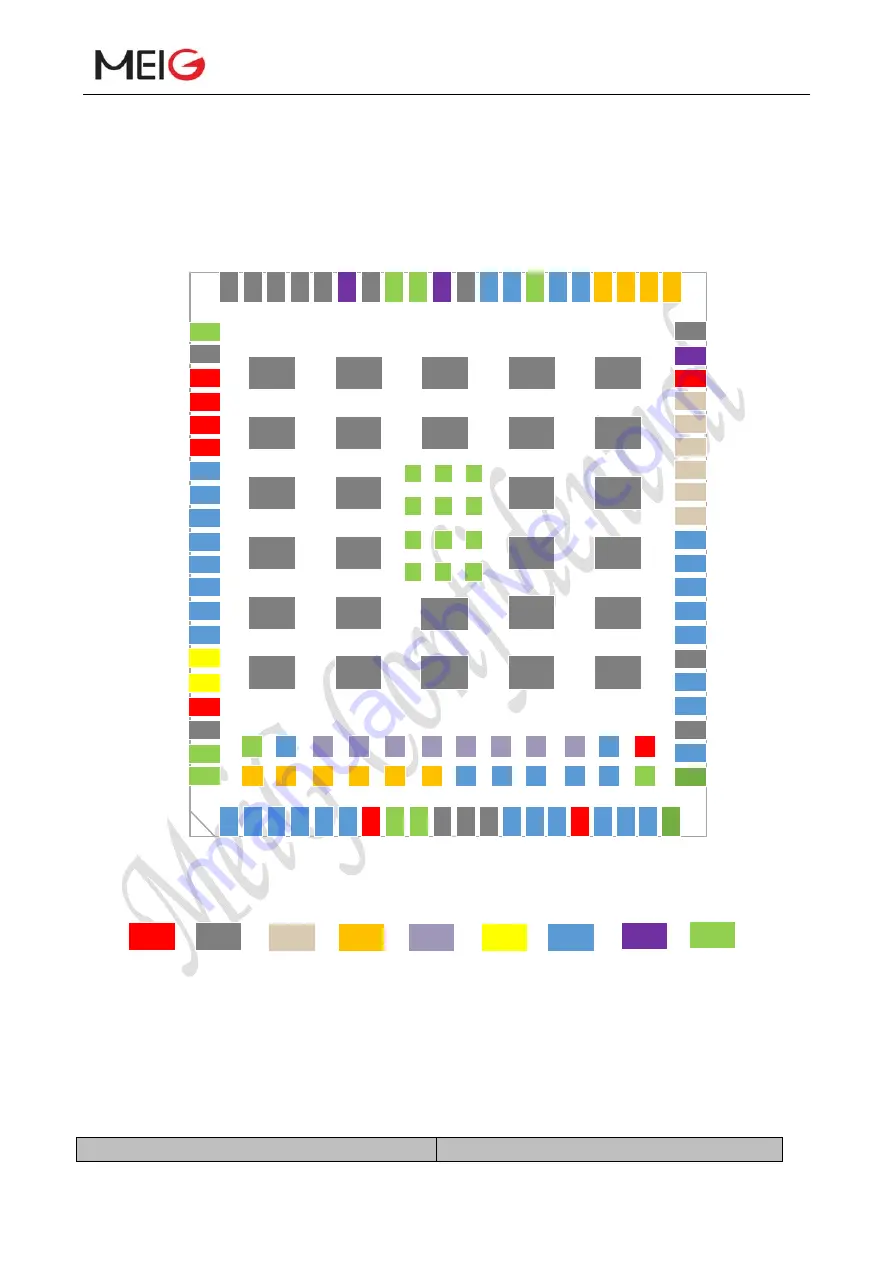

3.2 LCC Card Interface Definition

52

51

50

49

48

144

143

47

46

45

44

43

42

41

40

39

38

37

1

2

3

4

5

6

7

141

142

8

9

10

11

12

13

14

15

16

69

68

67

66

65

64

63

114

113

72

71

70

23

24

25

26

27

28

29

116

115

19

20

21

22

GND

POWER

WLAN&BT

USB

SGMII

Signals

ANT

Reserved

GN

D

GN

D

GN

D

AN

T_

M

A

IN

GN

D

Re

se

rv

e

d

Re

se

rv

e

d

GN

D

AD

C

0

AD

C

1

Re

se

rv

e

d

I2

C_S

D

A

I2

C_S

C

L

BT

_

C

T

S

BT

_

TX

D

BT

_

R

T

S

SD_DATA2

SD_DATA3

PCM_CLK

PCM_SYNC

PCM_OUT

USB_BOOT

Reserved

US

IM

_

C

LK

US

IM

_

D

A

TA

GN

D

US

IM

_

G

ND

US

IM

_

P

R

E

SE

N

C

E

US

IM

_

V

D

D

GN

D

DBG

_

RX

D

DBG

_

TX

D

Re

se

rve

d

VD

D

_

E

XT

NE

T

_

ST

A

T

U

S

NE

T

_

M

O

D

E

W_

D

IS

A

B

LE

#

W

A

K

EU

P

_O

U

T

_N

AP

_

R

E

A

D

Y

WAK

EU

P

_

IN

Reserved

GND

USB_VBUS

RXD

TXD

DCD

Reserved

CTS

USB_DP

DTR

RTS

USB_DM

17

18

36

35

34

33

32

31

30

GND

ANT_DIV

VDD_SDIO

SD_CMD

SD_CLK

SD_DATA0

61

60

59

58

57

56

55

62

54

53

US

IM

_

R

ST

SD_DATA1

PCM_IN

SD_INS_DET

GND

PWRKEY

RESET_N

GND

AN

T_

G

N

SS

GN

D

GN

D

RI

VBAT_BB

VBAT_BB

GND

Reserved

VBAT_RF

VBAT_RF

STATUS

85

86

87

88

89

73

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

74

75

76

79

82

129

130

131

132

133

134

135

136

137

138

139

140

77

78

80

81

83

84

117

118

119

120

121

122

123

124

125

126

127

128

BT

_

R

X

D

Re

se

rv

ed

W

LA

N

_S

LP

_C

LK

EP

H

Y

_R

ST

_N

EP

H

Y_I

NT

_N

SG

MI

I_

MD

A

TA

SG

MI

I_

MC

LK

SGM

II_

TX

_M

SG

M

II_

TX

_P

SG

M

II_

R

X_P

SGM

II_

RX

_M

PM

_E

N

A

B

LE

USI

M

2_

V

D

D

SD

C

1_

D

A

TA

3

SD

C

1_

D

A

TA

2

SD

C

1_

D

A

TA

1

SD

C

1_

D

A

TA

0

SD

C

1_

C

LK

SD

C

1_C

M

D

WA

KE

_O

N

_

WI

R

EL

ES

S

WL

A

N

_E

N

CO

EX

_U

A

R

T_

R

X

C

O

EX

_U

AR

T_

TX

BT

_E

N

SD

Re

se

rve

d

Re

se

rv

ed

Re

se

rve

d

Figure 2 Pin Assignment

3.3 Pin Description

The following table shows the SLM750’s pin definition.

Table 4: IO Parameters Definition

Type

Description