December 20, 2005

8

ddr_dq[3]

Data 3

J21

ddr_dq[4]

Data 4

M20

ddr_dq[5]

Data 5

K22

ddr_dq[6]

Data 6

N20

ddr_dq[7]

Data 7

J22

ddr_dq[8]

Data 8

T21

ddr_dq[9]

Data 9

P20

ddr_dq[10]

Data 10

T20

ddr_dq[11]

Data 11

T19

ddr_dq[12]

Data 12

U22

ddr_dq[13]

Data 13

P22

ddr_dq[14]

Data 14

U21

ddr_dq[15]

Data 15

U20

ddr_ba[0]

Bank Select 0

L23

ddr_ba[1]

Bank Select 1

M24

ddr_dm[0]

Write Mask0

M22

ddr_dm[1]

Write Mask1

N22

ddr_dqs[0]

Data Strobe0

M19

ddr_dqs[1]

Data Strobe1

N19

ddr_csn

Chip Select

L24

ddr_rasn

Row Address Strobe

M21

ddr_casn

Column Address Strobe

M23

ddr_wen

Write Enable

L21

ddr_clk

Clock

R20

ddr_clkn

Clock

R19

ddr_clke

Clock Enable

K21

3.3 Flash

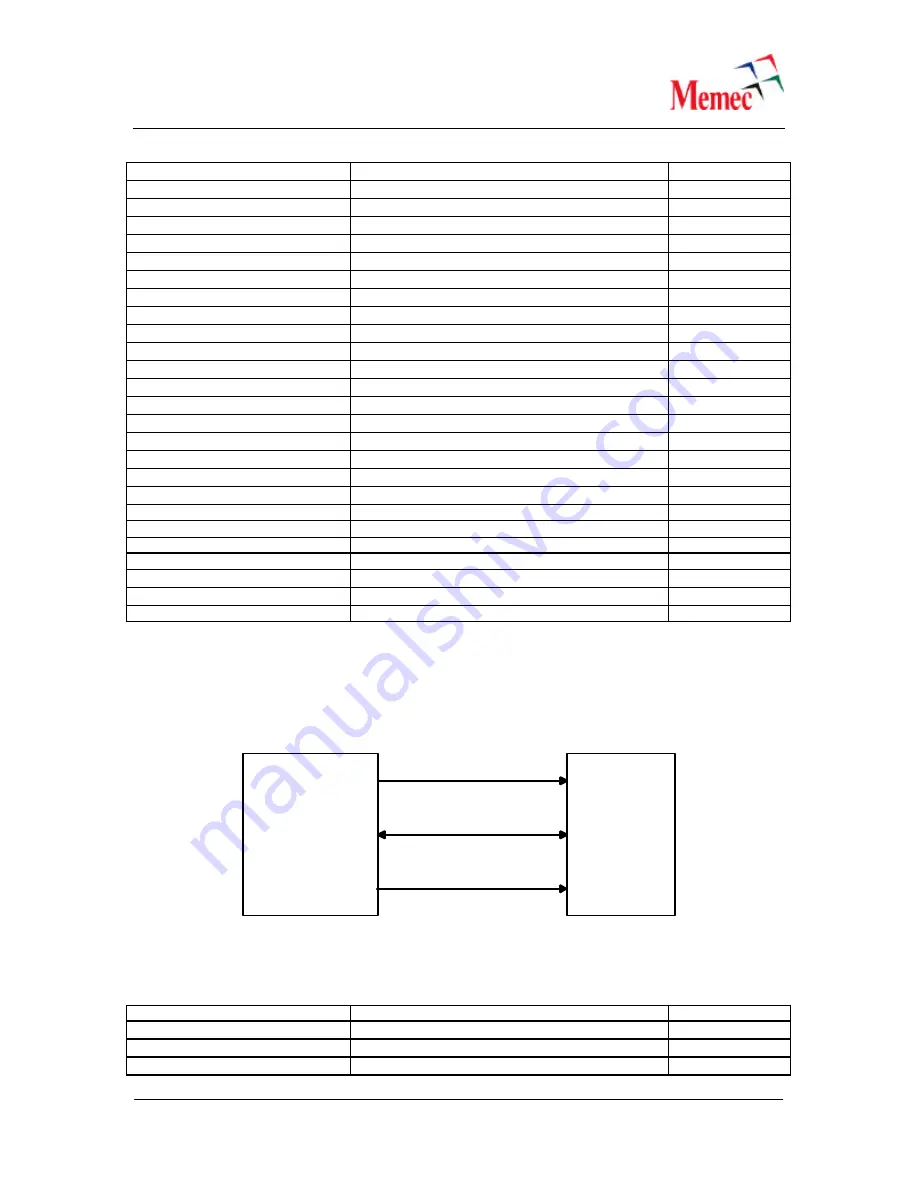

The Virtex-4™ MB development board provides 4MB of flash memory (x16). A high-level block

diagram of the flash interface is shown below followed by a table describing the flash memory

interface signals.

Virtex-4 FPGA

LX25-FF668

Flash

(4MB)

Control

Data[0:15]

Address[0:20]

Figure 5 – Flash Interface

Table 4 – Flash Interface Pin Assignments

Signal Name

Description

FPGA Pin #

flash_addr[0]

Address 0

M2

flash_addr[1]

Address 1

T6

flash_addr[2]

Address 2

R5