December 20, 2005

11

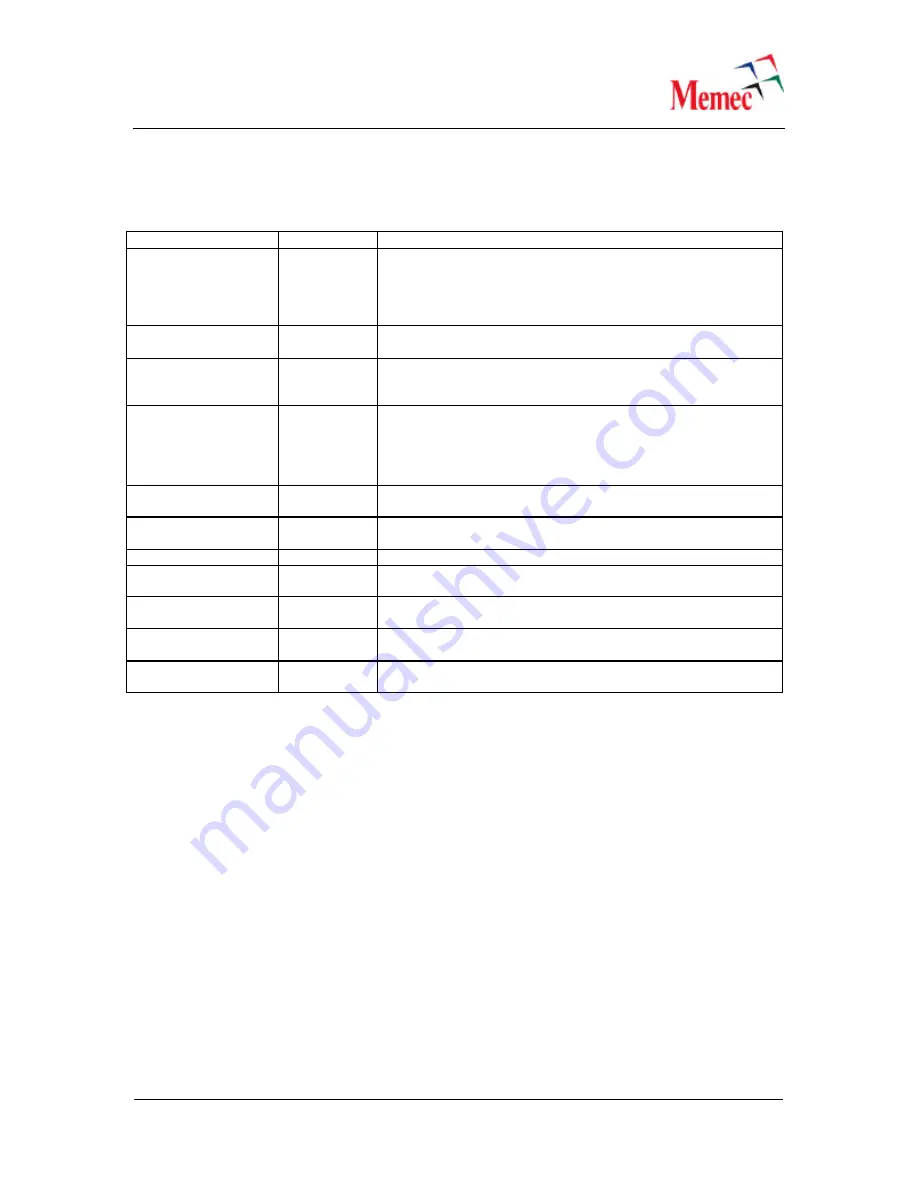

The following table provides a brief description of each clock input to the Virtex-4 FPGA.

Table 5 - Clock Inputs

Signal Name

FPGA Pin #

Description

CLK_PROG_P,

CLK_PROG_N

A10,

B10

Positive and Negative Differential System Clock Inputs

–

These clock inputs are connected to the output of an LVDS clock

synthesizer. This programmable clock source can generate a

clock frequency of 25 to 700MHz. Refer to the Programmable

LVDS Clock Source section for more information.

LIO_CLKIN_P,

LIO_CLKIN_N

B17,

A17

P240 Module Differential Clock Input

– This clock input is

connected to the P240 connector located on the Virtex-4 board.

LIO_CLKIN_0,

LIO_CLKIN_1

D12,

E13

P240 Module Single-ended Clock Input

s– These clock inputs

are connected to the P240 connector located on the Virtex-4

board.

SPI_RDCLK_P,

SPI_RDCLK _N

AF11,

AF10

Positive and Negative Differential SPI-4.2 Receive Clock

Inputs

– These clock inputs are connected to the LVDS receive

connector on the

Virtex-4 MB

board. For the SPI-4.2

applications, these clock inputs are the SPI-4.2 receive clock

outputs.

DDR_CLK

C15

DDR Feedback Clock Input

– This clock input is connected to

the DDR clock.

CLK_100

B13

System Clock

– This clock input is connected to a 100MHz

LVTTL oscillator.

CLK_SOCKET

AE14

LVTTL Clock Input

– LVTTL socket on the Virtex-4 board.

SPI_TSCLK

R8

SPI-4.2 Transmit Status Clock Input

– This clock input is

connected to the SPI-4.2 transmit status clock output.

ETH_RXC

A16

Ethernet Receive Clock Input

– This clock input is connected

to the Ethernet receive clock.

ETH_TXC

B15

Ethernet Transmit Clock Input

– This clock input is connected

to the Ethernet transmit clock.

SAM_CLK

AE10

SystemACE Module Clock Input

– This clock input is

connected to the SystemACE Module connector.

3.4.1 Programmable LVDS Clock Source

A programmable LVDS clock synthesizer is used on the Virtex-4 MB development board to

generate a reference clock input to the LVDS interface. The use of this variable clock source,

allows designers to prototype various interconnect technologies with different clock source

requirements. The differential output port is also well suited for DSP applications when driving

external DACs or ADCs.

3.4.2 ICS8442 Programmable LVDS Clock Synthesizer

The Virtex-4 MB development board design uses the ICS8442 LVDS clock synthesizer for

generating various clock frequencies. A list of features included in the ICS8442 device is shown

below.

•

Output frequency range: 25MHz to 700MHz

•

RMS period jitter: 2.7ps (typical)

•

Cycle-to-cycle jitter: 27ps (typical)

•

Output rise and fall time: 650ps (maximum)

•

Output duty cycle: 48/52