dsPIC30F6010

DS70119B-page 128

Advance Information

2004 Microchip Technology Inc.

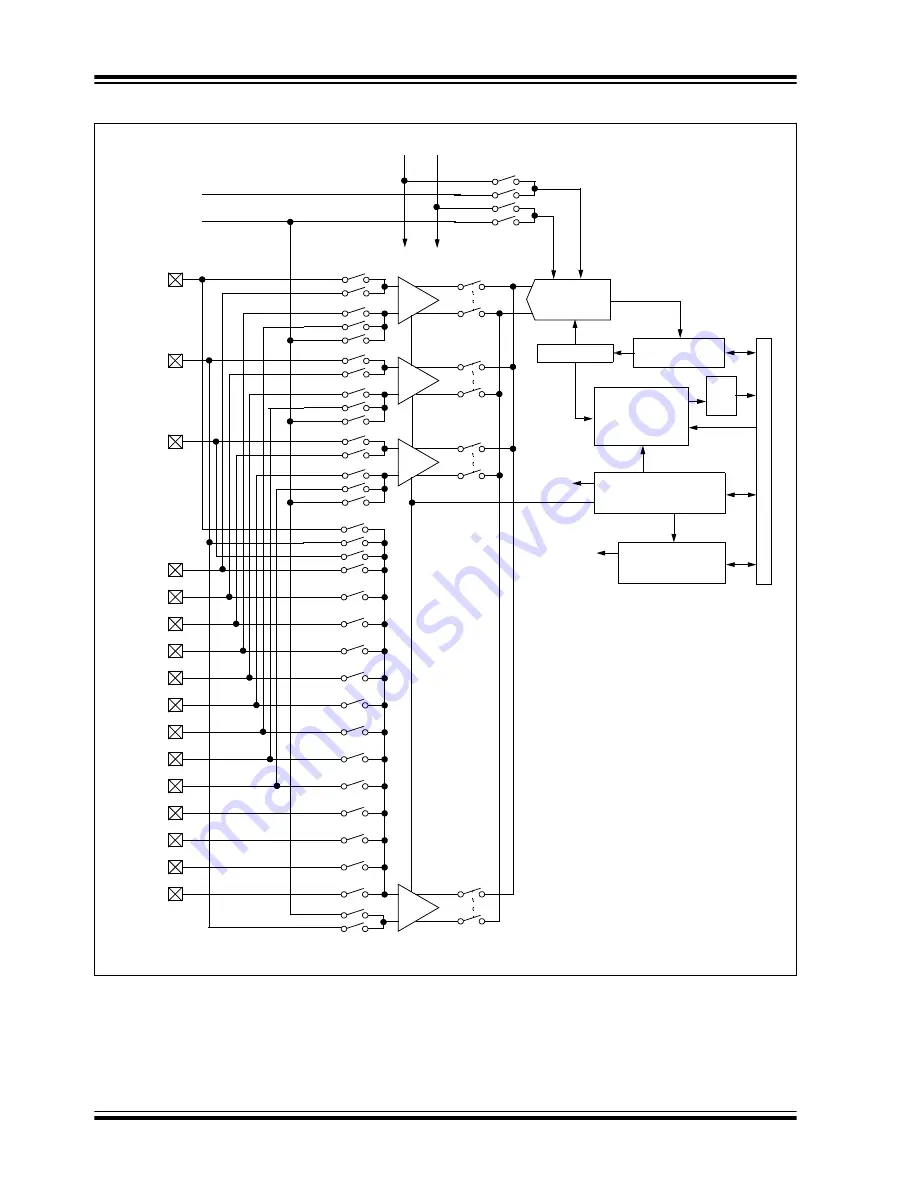

FIGURE 20-1:

10-BIT HIGH SPEED A/D FUNCTIONAL BLOCK DIAGRAM

S/H

+

-

10-bit Result

Conversion Logic

V

REF

+

AV

SS

AV

DD

ADC

Dat

a

16-word, 10-bit

Dual Port

Buffer

Bus Interface

AN12

AN0

AN5

AN7

AN9

AN13

AN14

AN15

AN12

AN1

AN2

AN3

AN4

AN6

AN8

AN10

AN11

AN13

AN14

AN15

AN8

AN9

AN10

AN11

AN4

AN5

AN6

AN7

AN0

AN1

AN2

AN3

CH1

CH2

CH3

CH0

AN5

AN2

AN11

AN8

AN4

AN1

AN10

AN7

AN3

AN0

AN9

AN6

AN1

V

REF

-

Sample/Sequence

Control

sample

CH1,CH2,

CH3,CH0

Input Mux

Control

input

switches

S/H

+

-

S/H

+

-

S/H

+

-

Format

Summary of Contents for dsPIC30F6010

Page 12: ...dsPIC30F6010 DS70119B page 10 Advance Information 2004 Microchip Technology Inc NOTES...

Page 32: ...dsPIC30F6010 DS70119B page 30 Advance Information 2004 Microchip Technology Inc NOTES...

Page 38: ...dsPIC30F6010 DS70119B page 36 Advance Information 2004 Microchip Technology Inc NOTES...

Page 50: ...dsPIC30F6010 DS70119B page 48 Advance Information 2004 Microchip Technology Inc NOTES...

Page 68: ...dsPIC30F6010 DS70119B page 66 Advance Information 2004 Microchip Technology Inc NOTES...

Page 72: ...dsPIC30F6010 DS70119B page 70 Advance Information 2004 Microchip Technology Inc NOTES...

Page 76: ...dsPIC30F6010 DS70119B page 74 Advance Information 2004 Microchip Technology Inc NOTES...

Page 86: ...dsPIC30F6010 DS70119B page 84 Advance Information 2004 Microchip Technology Inc NOTES...

Page 108: ...dsPIC30F6010 DS70119B page 106 Advance Information 2004 Microchip Technology Inc NOTES...

Page 116: ...dsPIC30F6010 DS70119B page 114 Advance Information 2004 Microchip Technology Inc NOTES...

Page 128: ...dsPIC30F6010 DS70119B page 126 Advance Information 2004 Microchip Technology Inc NOTES...

Page 150: ...dsPIC30F6010 DS70119B page 148 Advance Information 2004 Microchip Technology Inc NOTES...

Page 164: ...dsPIC30F6010 DS70119B page 162 Advance Information 2004 Microchip Technology Inc NOTES...

Page 208: ...dsPIC30F6010 DS70119B page 206 Advance Information 2004 Microchip Technology Inc NOTES...

Page 220: ...dsPIC30F6010 DS70119B page 220 Advance Information 2004 Microchip Technology Inc NOTES...

Page 221: ...2004 Microchip Technology Inc Advance Information DS70119B page 221 dsPIC30F6010 NOTES...