Schematics

2015

Microchip Technology Inc.

D

S

5

0002403A-p

age 37

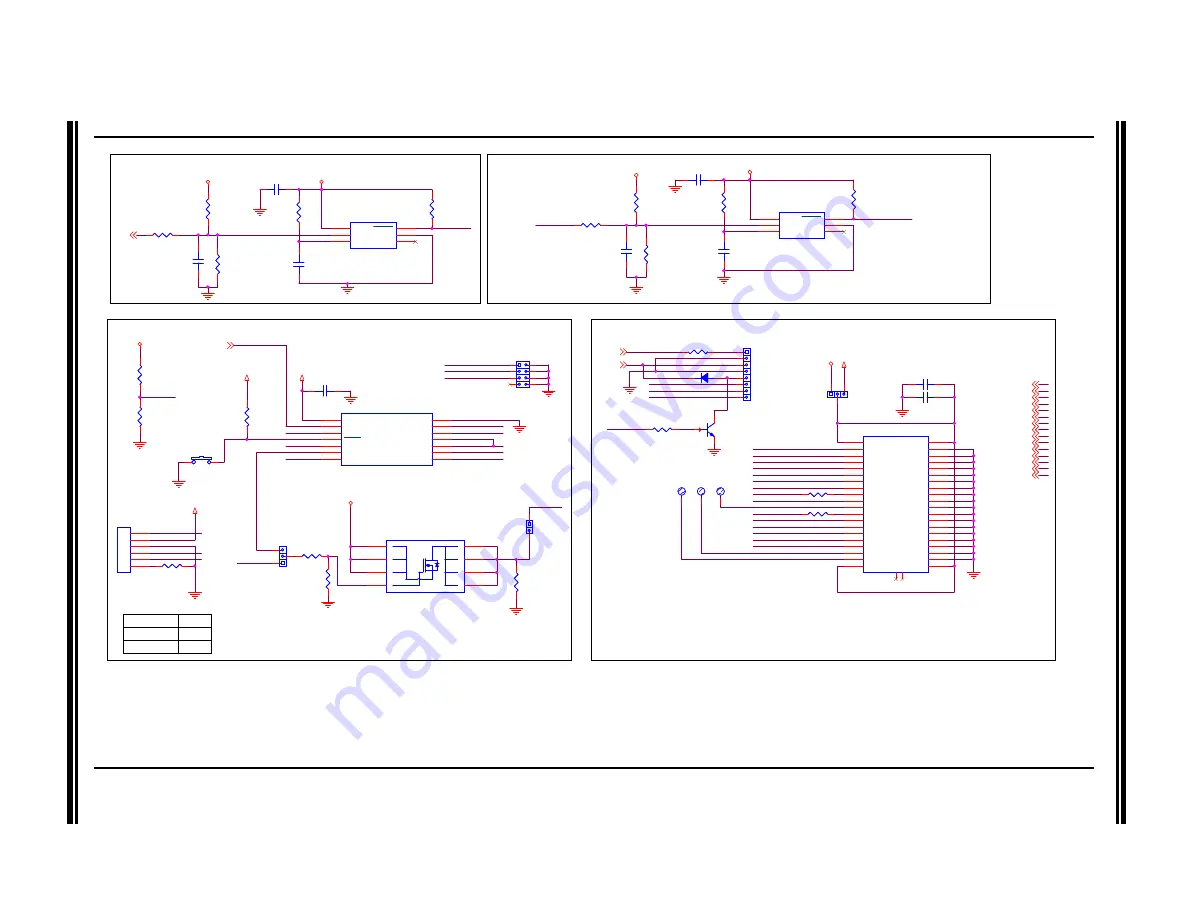

FIGURE B-10:

ENHANCED LINK DETECTION

Standard Link Detection

PHY Power sequencing with transceiver power Down/Reset

Standard Link Detection

PHY reset release delay with transceiver power Down/Reset

DNP

Enhanced Link Detection

uC detects auto-negotiation restart command and

power down PHY and transceiver / resets PHY and transceiver

MII Female for External PHY Board

Note:

Ethercat external board (Port2_TXER,COL,CRS signals not used)

External Port 2 Interface

Note:

Default open.

When used J79 DNP

200 mS

300 mS

500 mS

180mS=176.17nF

800mS=180.1nF

180mS=176.17nF

800mS=180.1nF

Link Detection selection

Standard

J79

Enhanced

Short 1&2

Short 2&3

(1-2*)

Link Detection Selection

5V

RST_Delay

MCLR

MCLR

ICSPDAT

ICSPCLK

ICSPDAT

ICSPCLK

MII_MDIO

RC2

MII_MDC

RC2

RC3

RC5

RC5

RA4

RC3

RC4

MII_MDIO

MII_RXD1

MII_TXD3

MII_RXER

MII_RXD3

MII_TXEN

MII_MDC

MII_RXD0

MII_TXD2

MII_TXD1

CRS

COL

MII_RXDV

MII_RXD2

MII_TXD0

MII_RXCLK

TXER

MII_CLK25

RST_Delay

5V_Delay

VCC_EXT0

5V_Delay

RC4

VCC_EXT0

RA4

RC4

3V3

5V

5V

5V

3V3

3V3

5V

3V3

3V3

3V3

VCC_EXT0

RST#

RST#

RST#

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_TXEN

MII_CLK25

MII_RXER

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXD3

MII_RXDV

MII_RXCLK

MII_MDIO

MII_MDC

MII_LINK

R157

100K

R157

100K

R147

10.0K

R147

10.0K

C80

DNP

C80

DNP

U9

NCP308SNADJT1G

U9

NCP308SNADJT1G

RESET

1

GND

2

MR

3

CT

4

SENSE

5

VDD

6

R163

100K

R163

100K

R148

1K

R148

1K

C77

0.1uF

C77

0.1uF

U8

NCP308SNADJT1G

U8

NCP308SNADJT1G

RESET

1

GND

2

MR

3

CT

4

SENSE

5

VDD

6

J29

J29

1

2

R152

ZERO

R152

ZERO

C81

DNP

C81

DNP

J25

J25

1

3

4

2

5

6

7

8

J27

5173277-2

J27

5173277-2

+5V4

40

GND1

39

GND2

38

GND3

37

GND4

36

GND5

35

GND6

34

GND7

33

GND8

32

GND9

31

GND10

30

GND11

29

GND12

28

GND13

27

GND14

26

GND15

25

GND16

24

GND17

23

GND18

22

+5V3

21

+5V1

1

MDIO

2

MDC

3

RXD3

4

RXD2

5

RXD1

6

RXD0

7

RX_DV

8

RX_CLK

9

RX_ER

10

TX_ER

11

TX_CLK

12

TX_EN

13

TXD0

14

TXD1

15

TXD2

16

TXD3

17

COL

18

CRS

19

+5V2

20

41

41

42

42

C82

10uF

C82

10uF

TP6

WHITE

TP6

WHITE

R156

100K

R156

100K

R161

33E

R161

33E

R153

374E

R153

374E

J28

DBG ICSP Header

J28

DBG ICSP Header

1

2

3

4

5

6

C78

0.001uF

C78

0.001uF

J26

J26

1

2

3

R162

1K

R162

1K

C83

0.1uF

C83

0.1uF

R159

1K

R159

1K

D8

IN4148

D8

IN4148

1

2

R154

374E

R154

374E

R149

ZERO

R149

ZERO

R165

10.0K

DNP

R165

10.0K

DNP

TP5

WHITE

TP5

WHITE

R155

ZERO

DNP

R155

ZERO

DNP

R151

ZERO

R151

ZERO

Q2

BC547

Q2

BC547

3

2

1

R150

10.0K

R150

10.0K

R160

33E

R160

33E

R158

4.7K

R158

4.7K

TP7

WHITE

TP7

WHITE

SW12

sw_pb_2P

SW12

sw_pb_2P

U10

PIC16F1824-I/ST

U10

PIC16F1824-I/ST

VDD

1

RA5

2

RA4

3

MCLR/VPP/RA3

4

RC5

5

RC4

6

RC3

7

VSS

14

RA0/ICSPDAT

13

RA1/ICSPCLK

12

RA2

11

RC0

10

RC1

9

RC2

8

R146

ZERO

R146

ZERO

J24

J24

1

2

3

4

5

6

7

8

C76

0.1uF

C76

0.1uF

U11

MCP87130

U11

MCP87130

S1

1

S2

2

S3

3

G

4

D1

8

D2

7

D4

5

D3

6

C84

0.1uF

C84

0.1uF

J30

J30

1

2

3

R145

1K

R145

1K

C79

0.001uF

C79

0.001uF

R164

ZERO

R164

ZERO