MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

119

•

No Activity clocks for Entry: 320

Memory Timing

•

Time To Hold Reset Before INIT - 67584 clks

•

MRD: 4 clks

•

RAS (Min): 8 clks

•

RAS (Max): 8192 clks

•

RCD: 6 clks

•

RP: 7 clks

•

REFI: 3104 clks

•

RC: 3 clks

•

XP: 3 clks

•

CKE: 3 clks

•

RFC: 79 clks

•

FAW: 0 clks

6.

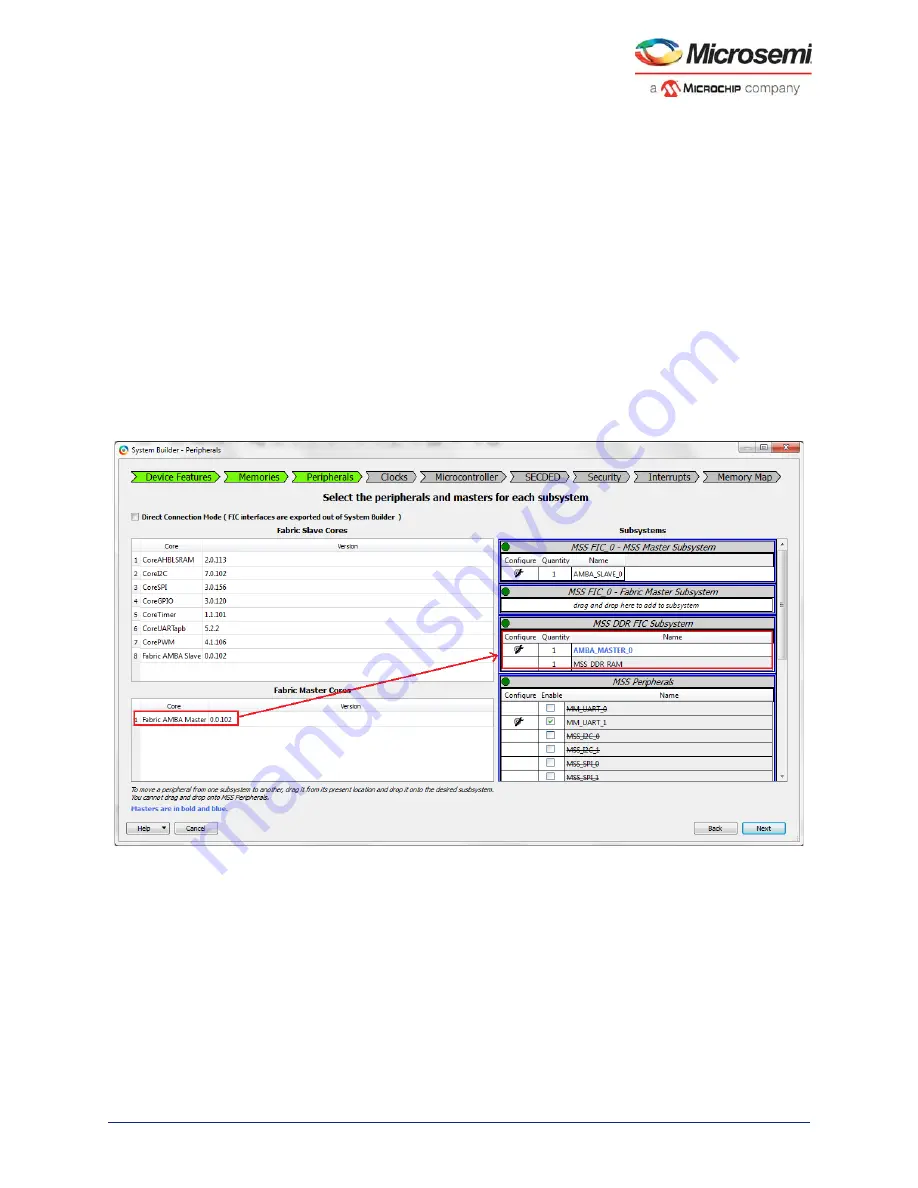

Navigate to the

Peripherals

tab. To access the MDDR from the FPGA fabric, drag and drop the

Fabric AMBA Master

to the

MSS DDR FIC Subsystem

and click

configure

to select the type of

interface as AXI or single AHB-Lite. The user logic in the FPGA fabric can access the DDR memory

through the MDDR using these interfaces. The following image shows the

Peripherals

tab.

Figure 52 •

MSS DDR FIC Subsystem Configuration

7.

Navigate to the

Clocks

tab. The

Clocks

tab allows to configure the system clock and subsystem

clocks. The MDDR subsystem operates on MDDR_CLK, which comes from MSS_CCC. The

MDDR_CLK must be selected as multiples of 1, 2, 3, 4, 6 or 8-of M3_CLK. The maximum frequency

of MDDR_CLK is 333.33 MHz. The following image shows the MDDR_CLK configuration.