MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

128

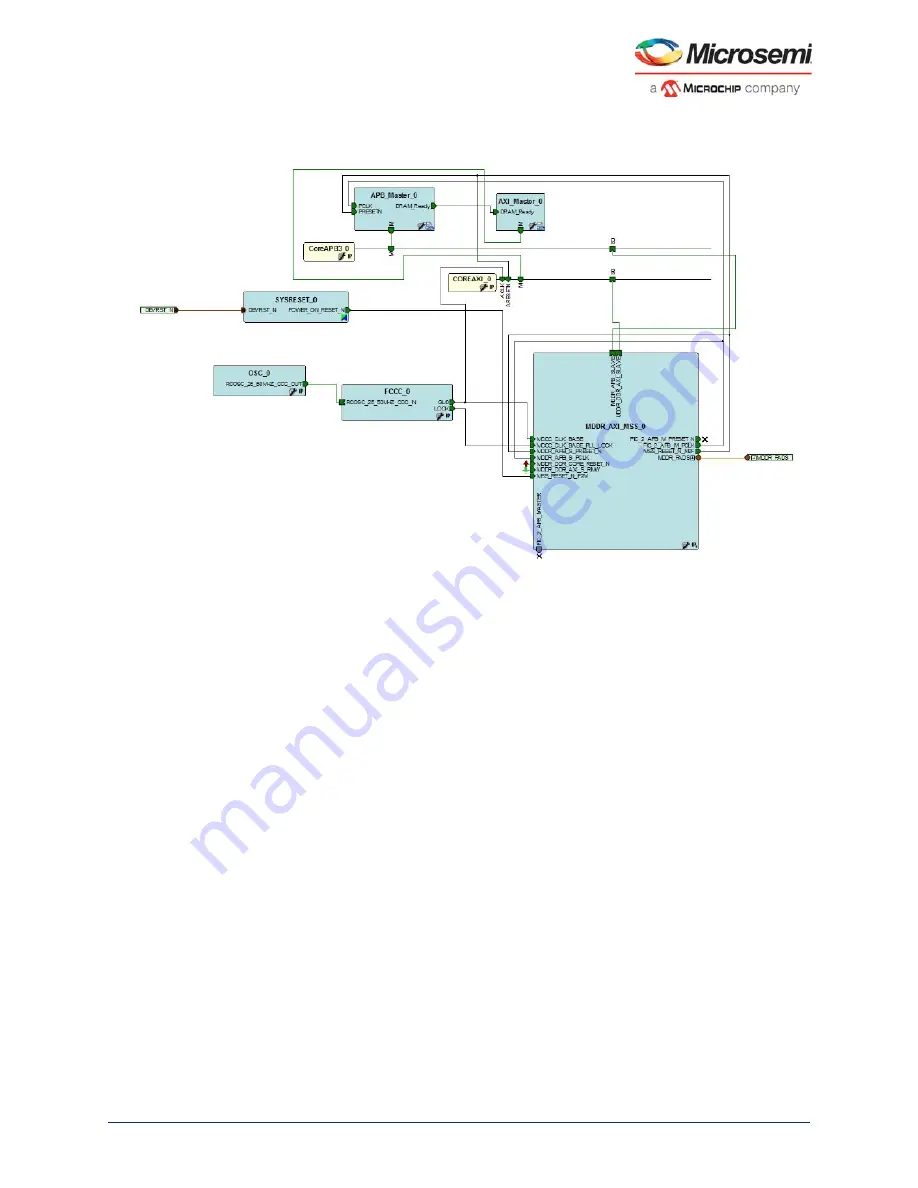

Make the other connections in the SmartDesign canvas, as shown in the following illustration.

Figure 67 •

SmartDesign Canvas

10. To verify the design in Libero SoC software, create a SmartDesign testbench project and instantiate

a DDR memory model provided by the DDR memory vendor. Simulate the design and observe the

AXI read and write transactions.

Note:

The MDDR subsystem can be configured using the Cortex-M3 processor without having an APB master.

The System Builder can be used to create the design by following steps in

. The System Builder provides "INIT_DONE" to indicate that the DDR

memory has been successfully initialized.

3.12.4

Use Model 2: Accessing MDDR from FPGA Fabric Through the

AHB Interface

The MDDR subsystem can be used to access the DDR memory, as shown in the following illustration.

The MDDR register can be configured through the MSS or user logic (AHB master) in the FPGA fabric.