Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

170

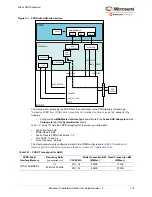

Figure 95 •

Clocks Configuration

10. Navigate to the

Memory Map

tab giving the required data in the rest of the

System Builder

tabs.

11. Instantiate the user AXI master logic in the SmartDesign canvas to access the FDDR through the

AXI interface. Make sure that the AXI master logic accesses the FDDR after configuring the FDDR

registers.

12. Instantiate the CCC block in the SmartDesign canvas and configure it to generate 111 MHz clock.

13. Connect the AXI_Master logic signals as follows:

•

CLK to GL0 of FCCC_0 and FDDR_SUBSYSTEM_CLK

•

LOCK to LOCK of FCCC_0 and FDDR_SUBSYSTEM_LOCK

•

RESET_N to INIT_DONE of FDDR_AXI_0

•

AXI_S_RMW to FDDR_AXI_S_RMW of FDDR_AXI_0 block

14. The following illustration shows the rest of the connections in the top level design.