Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

176

4.9.1

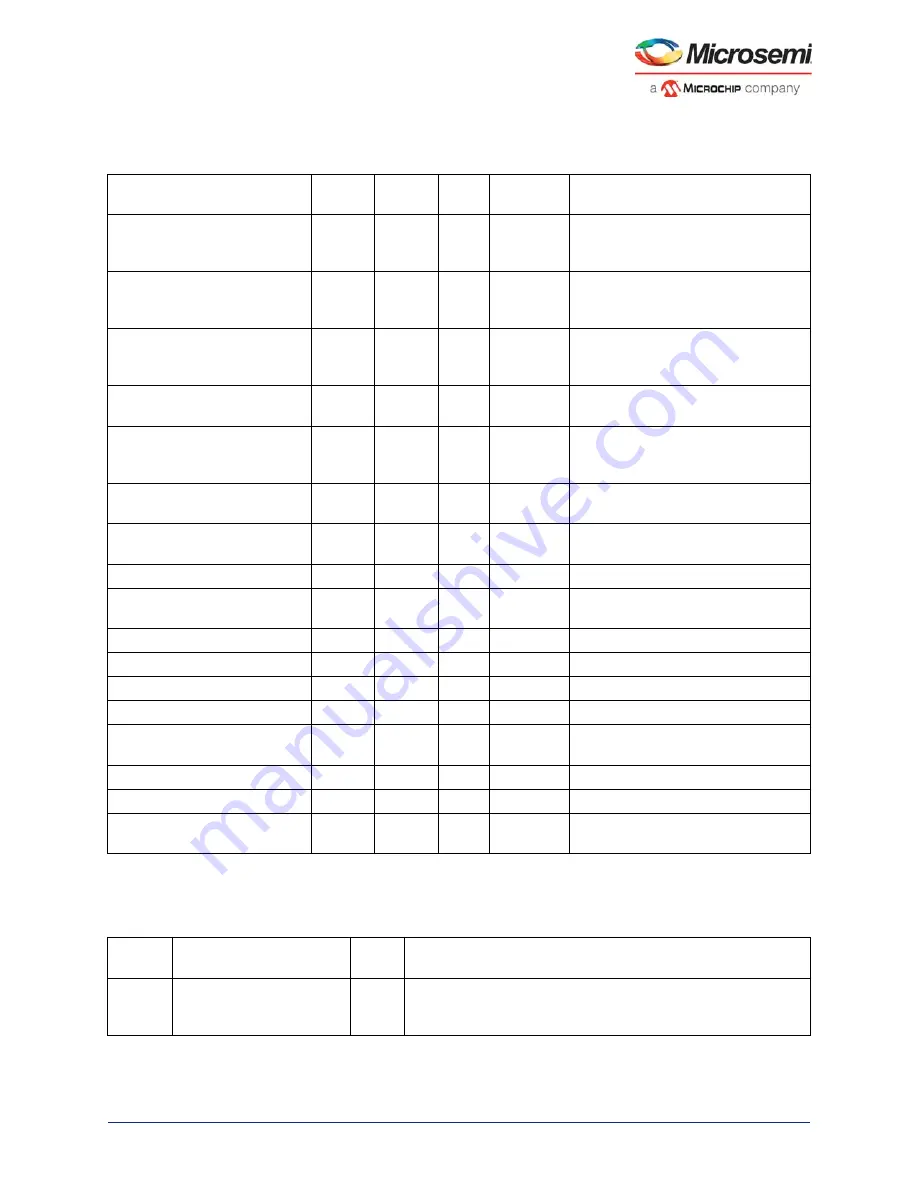

FDDR SYSREG Configuration Register Summary

4.9.2

FDDR SYSREG Configuration Register Bit Definitions

Table 143 •

FDDR SYSREG

Register Name

Address

Offset

Register

Type

Flash

Reset

Source

Description

0x500

RW

P

PRESETN

Comes from SYSREG. Controls the

corresponding configuration input of

the FPLL.

0x504

RW

P

PRESETN

Comes from SYSREG. Controls the

corresponding configuration input of

the FPLL.

0x508

RW

P

PRESETN

Comes from SYSREG. Controls the

corresponding configuration input of

the FPLL.

0x50C

RW

P

PRESETN

Enables the clock to the DDR memory

controller.

0x510

RW

P

PRESETN

Selects the standby glitch-free

multiplexers within the fabric alignment

clock controller (FACC).

0x514

RW

P

PRESETN

Selects the ratio between CLK_A and

CLK_DDR_FIC.

0x518

RW

P

PRESETN

Selects the delay values to be added to

the FPLL.

0x51C

RW

P

PRESETN

Soft reset register for FDDR

0x520

RW

P

PRESETN

Configurations register for DDRIO

calibration block

0x524

RW

P

PRESETN

Interrupt enable register

0x528

RW

P

PRESETN

Selects AXI/AHB interface in the fabric.

0x52C

RW

P

PRESETN

Automatic calibration lock is enabled.

0x530

RO

–

PRESETN

Indicates the lock status of the fPLL.

0x534

RO

–

PRESETN

Indicates the lock status of the fabric

PLL.

0x53C

RO

–

PRESETN

Interrupt status register

0x544

RO

–

PRESETN

I/O calibration status register

0x548

RW

P

PRESETN

Reset to fabric portion of the fabric

alignment test circuit

Table 144 •

PLL_CONFIG_LOW_1

Bit

Number Name

Reset

Value

Description

[31:16]

Reserved

0×0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should

be preserved across a read-modify-write operation.