Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

194

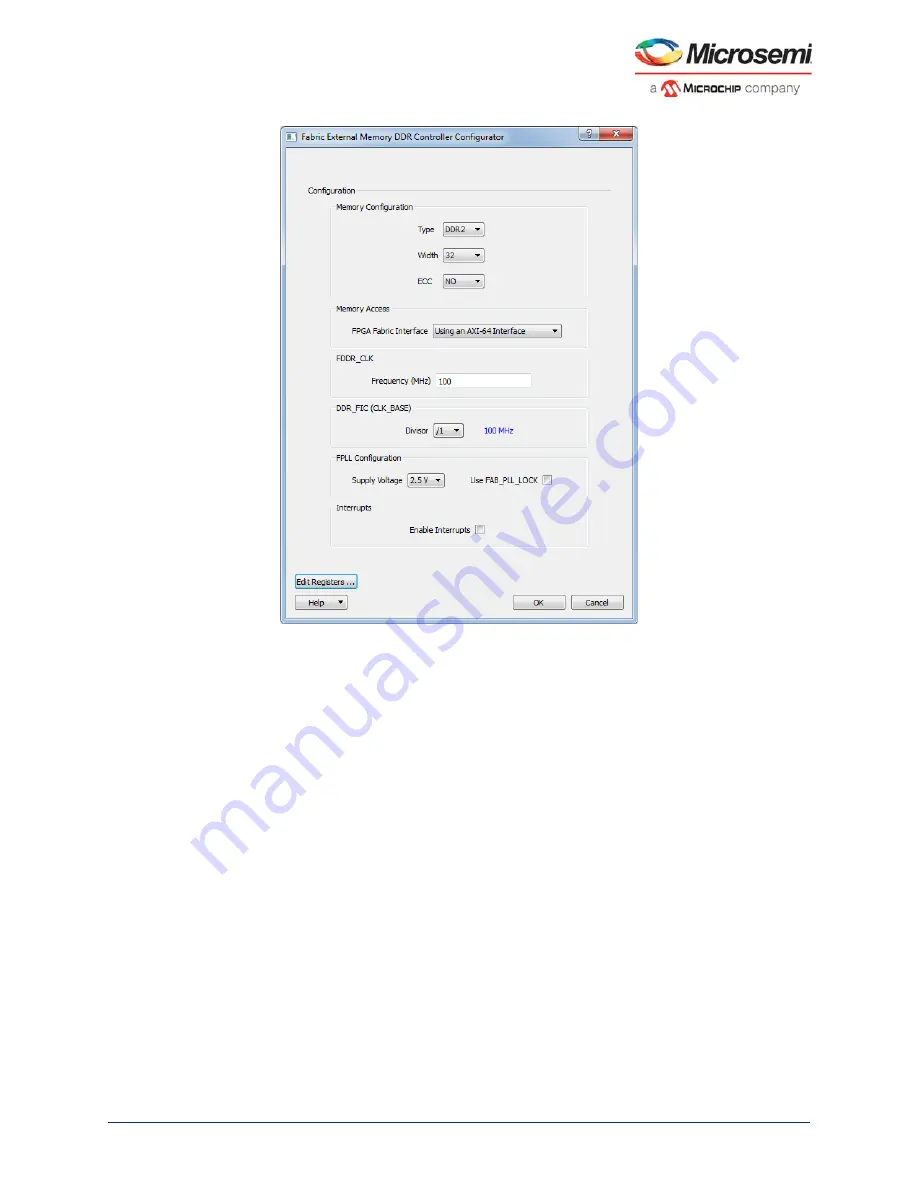

Figure 110 •

Fabric External Memory DDR Controller Configurator

Depending on the application requirement, select the memory settings under the General tab as shown

in the image.

•

Memory Type can be selected as DDR2, DDR3 or LPDDR.

•

The Data width can be selected as 32-bit, 16-bit, or 8-bit. Refer Table 1-13 for supported data widths

for various SmartFusion2 device packages.

•

Clock Frequency can be selected between 20 MHz to 333MHz. The FDDR subsystem operates on

this clock (FDDR_CLK) frequency

•

The SECDED (ECC) can be enabled or disabled.

Select

FPGA Fabric Interface

type as AXI, single AHBLite, or two AHBLite. On completion of the

configuration, the selected interface is exposed in SmartDesign. User logic in the FPGA fabric can

access DDR memory through the FDDR using these interfaces.

The DDR_FIC clock drives the DDR_FIC slave interface and defines the frequency at which the FPGA

fabric subsystem connected to this interface is intended to run. DDR_FIC clock can be configured using

FDDR CLOCK Divisor—1, 2, 3, 4, 6, 8, 12, or 16—of FDDR_CLK. The maximum frequency of DDR_FIC

clock is 200 MHz. The DDR_FIC clock has to be driven from FPGA fabric.

The FPLL LOCK signal can be exposed to the FPGA fabric to monitor the health of the PLL (loss of lock

requires special handling by the application).

The interrupts in the FDDR subsystem can be exposed in SmartDesign by selecting the

Enable

Interrupts

check box.

Select the memory settings under

Memory Initialization

tab and

Memory Timing

tab as described in

the steps 3 and 4 in the

"Design Flow Using System Builder" section on page 184

.