MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

42

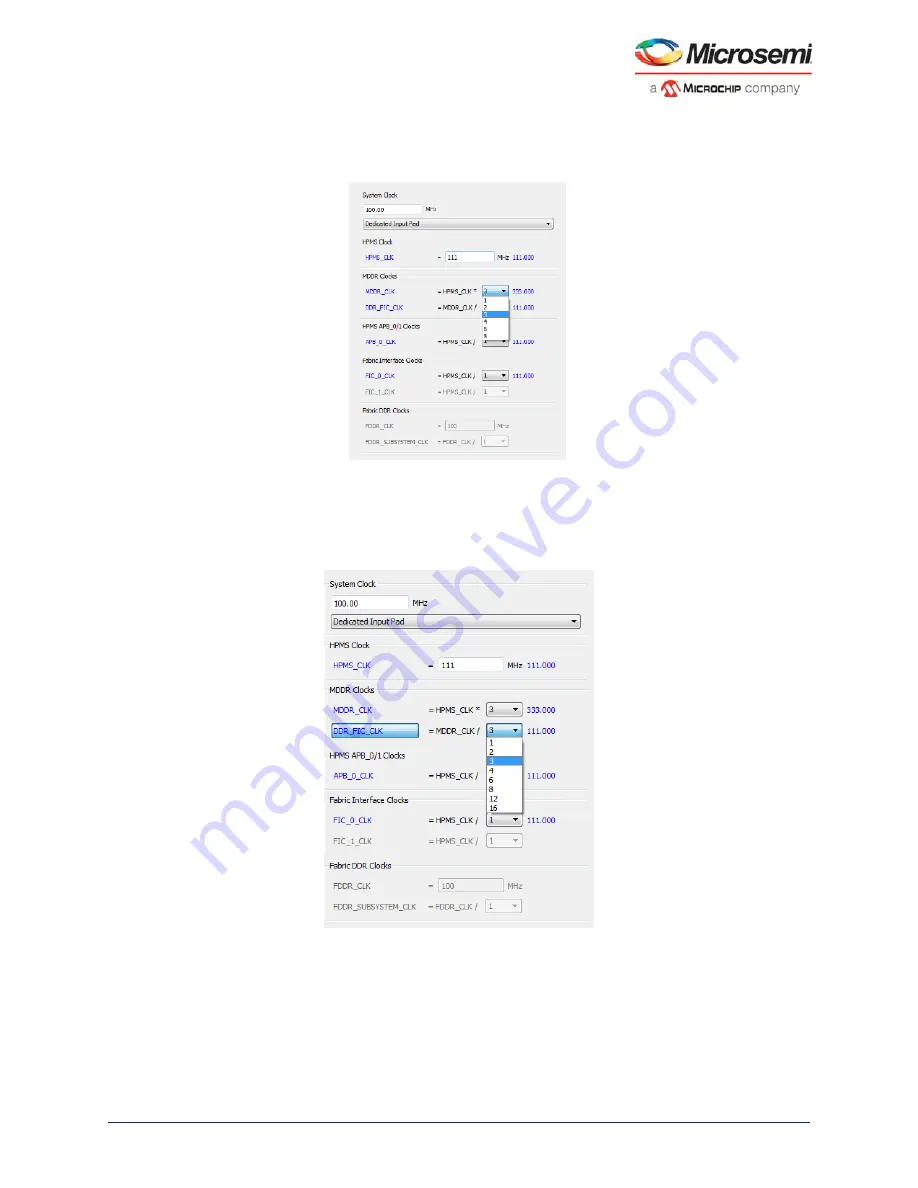

The MDDR_CLK must be selected as multiples of 1, 2, 3, 4, 6, or 8 of HPMS_CLK. This clock can

be configured using the HPMS_CCC configurator. The maximum frequency of MDDR_CLK is

333.33 MHz. The following illustration shows the MDDR_CLK configuration.

Figure 18 •

MDDR_CLK Configuration

DDR_FIC_CLK drives the DDR_FIC slave interface and defines the frequency at which the FPGA fabric

subsystem connected to this interface is intended to run. DDR_FIC_CLK can be configured as a ratio of

MDDR_CLK (1, 2, 3, 4, 6, 8, 12, 16, or 32) using the Clocks configurator. The maximum frequency of

DDR_FIC_CLK is 200 MHz. The following illustration shows the DDR_FIC_CLK configuration.

Figure 19 •

DDR_FIC_CLK Configuration

If the MDDR_CLK ratio to HPMS_CLK is a multiple of 3, DDR_FIC_CLKs ratio to MDDR_CLK must also

be a multiple of 3, and vice versa. The configuration issues an error if this requirement is not met. This

limitation is imposed by the internal implementation of the HPMS CCC.

3.6.1.1

I/O Configuration

In the

I/O Editor

window, as shown in the following illustration, configure I/O settings such as ODT and

drive strength.